# MCP6V01/2/3

# 300 µA, Auto-Zeroed Op Amps

#### **Features**

- · High DC Precision:

- V<sub>OS</sub> Drift: ±50 nV/°C (maximum)

- V<sub>OS</sub>: ±2 μV (maximum)

- A<sub>OL</sub>: 130 dB (minimum)

- PSRR: 130 dB (minimum)

- CMRR: 130 dB (minimum)

- $E_{ni}$ : 2.5  $\mu$ V<sub>P-P</sub> (typical), f = 0.1 Hz to 10 Hz

- $E_{ni}$ : 0.79  $\mu$ Vp-p (typical), f = 0.01 Hz to 1 Hz

- · Low Power and Supply Voltages:

- I<sub>Ω</sub>: 300 μA/amplifier (typical)

- Wide Supply Voltage Range: 1.8V to 5.5V

- · Easy to Use:

- Rail-to-Rail Input/Output

- Gain Bandwidth Product: 1.3 MHz (typical)

- Unity Gain Stable

- Available in Single and Dual

- Single with Chip Select (CS): MCP6V03

- Extended Temperature Range: -40°C to +125°C

## **Typical Applications**

- · Portable Instrumentation

- · Sensor Conditioning

- · Temperature Measurement

- · DC Offset Correction

- · Medical Instrumentation

#### **Design Aids**

- · SPICE Macro Models

- FilterLab<sup>®</sup> Software

- Mindi™ Circuit Designer & Simulator

- · Microchip Advanced Part Selector (MAPS)

- · Analog Demonstration and Evaluation Boards

- · Application Notes

#### **Related Parts**

• MCP6V06/7/8: Non-spread clock, lower noise

#### **Description**

The Microchip Technology Inc. MCP6V01/2/3 family of operational amplifiers has input offset voltage correction for very low offset and offset drift. These devices have a wide gain bandwidth product (1.3 MHz, typical) and strongly reject switching noise. They are unity gain stable, have no 1/f noise, and have good PSRR and CMRR. These products operate with a single supply voltage as low as 1.8V, while drawing 300 µA/amplifier (typical) of quiescent current.

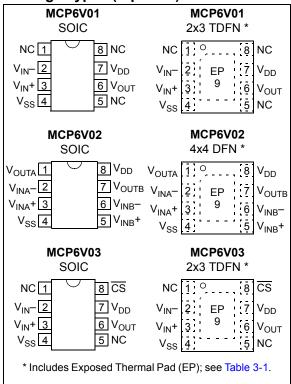

The Microchip Technology Inc. MCP6V01/2/3 op amps are offered in single (MCP6V01), single with Chip Select (CS) (MCP6V03), and dual (MCP6V02). They are designed in an advanced CMOS process.

#### Package Types (top view)

#### 1.0 ELECTRICAL CHARACTERISTICS

#### 1.1 Absolute Maximum Ratings †

| V <sub>DD</sub> - V <sub>SS</sub>                      | 6.5V                                    |

|--------------------------------------------------------|-----------------------------------------|

| Current at Input Pins                                  | ±2 mA                                   |

| Analog Inputs ( $V_{IN}$ + and $V_{IN}$ -) †† $V_{SS}$ | $_{\rm S}$ – 1.0V to $V_{\rm DD}$ +1.0V |

| All other Inputs and OutputsVSS                        | $_{\rm S}$ – 0.3V to $V_{\rm DD}$ +0.3V |

| Difference Input voltage                               | V <sub>DD</sub> – V <sub>SS</sub>       |

| Output Short Circuit Current                           | Continuous                              |

| Current at Output and Supply Pins                      | ±30 mA                                  |

| Storage Temperature                                    | 65°C to +150°C                          |

| Max. Junction Temperature                              | +150°C                                  |

| ESD protection on all pins (HBM, MM)                   | ≥ 4 kV, 300V                            |

|                                                        |                                         |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

†† See Section 4.2.1 "Rail-to-Rail Inputs".

#### 1.2 Specifications

#### TABLE 1-1: DC ELECTRICAL SPECIFICATIONS

**Electrical Characteristics:** Unless otherwise indicated,  $T_A$  = +25°C,  $V_{DD}$  = +1.8V to +5.5V,  $V_{SS}$  = GND,  $V_{CM}$  =  $V_{DD}/3$ ,  $V_{OUT} = V_{DD}/2$ ,  $V_L = V_{DD}/2$ ,  $R_L = 20 \text{ k}\Omega$  to  $V_L$ , and  $\overline{CS} = \overline{GND}$  (refer to Figure 1-5 and Figure 1-6). **Parameters** Sym Min Typ Max Units Conditions Input Offset Input Offset Voltage  $V_{\text{OS}}$ -2.0 +2.0 μV  $T_A = +25^{\circ}C$  (Note 1) nV/°C Input Offset Voltage Drift with Temperature -50  $T_A = -40 \text{ to } +125^{\circ}\text{C}$ TC<sub>1</sub> +50 (Note 1) (linear Temp. Co.)  $T_A = -40 \text{ to } +125^{\circ}\text{C}$ Input Offset Voltage Quadratic Temp. Co.  $TC_2$ +0.1 nV/°C2 **PSRR** Power Supply Rejection 130 143 (Note 1) Input Bias Current and Impedance Input Bias Current ±1 Αq  $I_B$  $T_A = +85^{\circ}C$ Input Bias Current across Temperature pΑ  $I_B$ 600 5000  $T_A = +125^{\circ}C$  $I_B$ pΑ Input Offset Current los -30 pΑ -50 Input Offset Current across Temperature  $T_A = +85^{\circ}C$  $I_{OS}$ -1000 -75 1000  $T_A = +125^{\circ}C$  $I_{OS}$ Common Mode Input Impedance 10<sup>13</sup>||6  $Z_{CM}$  $\Omega || pF$ 10<sup>13</sup>||6 Differential Input Impedance  $\Omega$ ||pF Z<sub>DIFF</sub> **Common Mode** Common-Mode Input Voltage Range V<sub>DD</sub> + 0.20  $V_{SS} - 0.20$ (Note 2)  $V_{CMR}$ Common-Mode Rejection **CMRR** 130 142 dΒ  $V_{DD} = 1.8V,$  $V_{CM} = -0.2V \text{ to } 2.0V$ (Note 1, Note 2)  $V_{DD} = 5.5V,$ **CMRR** 140 152 dΒ  $V_{CM} = -0.2V \text{ to } 5.7V$ (Note 1, Note 2) Open-Loop Gain DC Open-Loop Gain (large signal) 130 145 dB  $V_{DD} = 1.8V,$  $A_{OL}$  $V_{OUT}$  = 0.2V to 1.6V (Note 1)  $A_{OL}$ 140 156 dB  $V_{DD} = 5.5V$ ,  $V_{OUT} = 0.2V \text{ to } 5.3V \text{ (Note 1)}$

Note 1: Set by design and characterization. Due to thermal junction and other effects in the production environment, these parts can only be screened in production (except TC<sub>1</sub>; see **Appendix B: "Offset Related Test Screens"**).

<sup>2:</sup> Figure 2-18 shows how V<sub>CMR</sub> changed across temperature for the first three production lots.

#### TABLE 1-1: DC ELECTRICAL SPECIFICATIONS (CONTINUED)

**Electrical Characteristics:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +1.8V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{CM} = V_{DD}/3$ ,  $V_{OUT} = V_{DD}/2$ ,  $V_L = V_{DD}/2$ ,  $R_L = 20 \text{ k}\Omega$  to  $V_L$ , and  $\overline{CS} = \overline{GND}$  (refer to Figure 1-5 and Figure 1-6). **Units Conditions Parameters** Sym Min Typ Max Output Maximum Output Voltage Swing G = +2, 0.5V input overdrive m۷ Vol, Voh  $V_{SS} + 15$ V<sub>DD</sub> – 15 **Output Short Circuit Current** ±7 mA  $V_{DD} = 1.8V$  $I_{SC}$  $V_{DD} = 5.5V$ ±22 mΑ I<sub>SC</sub> **Power Supply**  $V_{DD}$ Supply Voltage 1.8 5.5 ٧ Quiescent Current per amplifier 200 300 400  $I_Q$ μΑ  $I_{\Omega} = 0$ POR Trip Voltage  $V_{POR}$ 1.15 1.65

#### TABLE 1-2: AC ELECTRICAL SPECIFICATIONS

**Electrical Characteristics:** Unless otherwise indicated,  $T_A = +25^{\circ}C$ ,  $V_{DD} = +1.8V$  to +5.5V,  $V_{SS} = GND$ ,  $V_{CM} = V_{DD}/3$ ,  $V_{OUT} = V_{DD}/2$ ,  $V_L = V_{$ Min Max Units **Conditions Parameters** Sym Typ Amplifier AC Response Gain Bandwidth Product **GBWP** 1.3 MHz Slew Rate SR 0.5 V/µs Phase Margin PM 65 G = +1**Amplifier Noise Response** E<sub>ni</sub> Input Noise Voltage 0.79 f = 0.01 Hz to 1 Hz  $\mu V_{P-P}$ 2.5 f = 0.1 Hz to 10 Hz Eni  $\mu V_{P-P}$ Input Noise Voltage Density e<sub>ni</sub> 120 nV/√Hz f < 2.5 kHz e<sub>ni</sub> 45 nV/√Hz f = 100 kHzInput Noise Current Density fA/√Hz 0.6 i<sub>ni</sub> Amplifier Distortion (Note 1) Intermodulation Distortion (AC) IMD <1  $\mu V_{PK}$  $V_{CM}$  tone = 50 m $V_{PK}$  at 1 kHz,  $G_N$  = 1,  $V_{DD}$  = 1.8V **IMD** <1  $\mu V_{PK}$  $V_{CM}$  tone = 50 m $V_{PK}$  at 1 kHz,  $G_N$  = 1,  $V_{DD}$  = 5.5VAmplifier Step Response Start Up Time 500 V<sub>OS</sub> within 50 μV of its final value  $t_{STR}$ μs G = +1,  $V_{IN}$  step of 2V, Offset Correction Settling Time 300 t<sub>STL</sub> μs V<sub>OS</sub> within 50 μV of its final value Output Overdrive Recovery Time 100 G = -100,  $\pm 0.5$ V input overdrive to  $V_{DD}/2$ ,  $t_{ODR}$ V<sub>IN</sub> 50% point to V<sub>OUT</sub> 90% point (Note 2)

**Note 1:** Set by design and characterization. Due to thermal junction and other effects in the production environment, these parts can only be screened in production (except TC<sub>1</sub>; see **Appendix B: "Offset Related Test Screens"**).

<sup>2:</sup> Figure 2-18 shows how V<sub>CMR</sub> changed across temperature for the first three production lots.

Note 1: These parameters were characterized using the circuit in Figure 1-7. Figure 2-37 and Figure 2-38 show both an IMD tone at DC and a residual tone at1 kHz; all other IMD and clock tones are spread by the randomization circuitry.

<sup>2:</sup> t<sub>ODR</sub> includes some uncertainty due to clock edge timing.

TABLE 1-3: DIGITAL ELECTRICAL SPECIFICATIONS

| Parameters Sum Min Tun May Unite Conditions |                     |                    |                                  |             |       |                                                                                                |  |  |

|---------------------------------------------|---------------------|--------------------|----------------------------------|-------------|-------|------------------------------------------------------------------------------------------------|--|--|

| Parameters                                  | Sym                 | Min                | Тур                              | Max         | Units | Conditions                                                                                     |  |  |

| CS Pull-Down Resistor (MCP6V03)             |                     |                    |                                  |             |       |                                                                                                |  |  |

| CS Pull-Down Resistor                       | R <sub>PD</sub>     | 3                  | 5                                | _           | ΜΩ    |                                                                                                |  |  |

| CS Low Specifications (MCP6V03)             |                     |                    |                                  |             |       |                                                                                                |  |  |

| CS Logic Threshold, Low                     | $V_{IL}$            | V <sub>SS</sub>    | _                                | $0.3V_{DD}$ | V     |                                                                                                |  |  |

| CS Input Current, Low                       | I <sub>CSL</sub>    | _                  | 5                                | _           | pА    | CS = V <sub>SS</sub>                                                                           |  |  |

| CS High Specifications (MCP6V03)            |                     |                    |                                  |             |       |                                                                                                |  |  |

| CS Logic Threshold, High                    | V <sub>IH</sub>     | 0.7V <sub>DD</sub> | _                                | $V_{DD}$    | V     |                                                                                                |  |  |

| CS Input Current, High                      | I <sub>CSH</sub>    | _                  | V <sub>DD</sub> /R <sub>PD</sub> | _           | pА    | CS = V <sub>DD</sub>                                                                           |  |  |

| CS Input High, GND Current per              | I <sub>SS</sub>     | _                  | -0.7                             | _           | μA    | $\overline{\text{CS}} = \text{V}_{\text{DD}}, \text{V}_{\text{DD}} = 1.8\text{V}$              |  |  |

| amplifier                                   | I <sub>SS</sub>     | _                  | -2.3                             | _           | μA    | $\overline{\text{CS}} = \text{V}_{\text{DD}}, \text{V}_{\text{DD}} = 5.5\text{V}$              |  |  |

| Amplifier Output Leakage, CS High           | I <sub>O_LEAK</sub> | _                  | 20                               | _           | pА    | CS = V <sub>DD</sub>                                                                           |  |  |

| CS Dynamic Specifications (MCP              | 6V03)               |                    |                                  |             | •     |                                                                                                |  |  |

| CS Low to Amplifier Output On               | t <sub>ON</sub>     | _                  | 11                               | 100         | μs    | $\overline{\text{CS}} \text{ Low} = \text{V}_{\text{SS}} + 0.3 \text{ V, G} = +1 \text{ V/V,}$ |  |  |

| Turn-on Time                                |                     |                    |                                  |             |       | $V_{OUT} = 0.9 V_{DD}/2$                                                                       |  |  |

| CS High to Amplifier Output High-Z          | t <sub>OFF</sub>    | _                  | 10                               | _           | μs    | $\overline{\text{CS}}$ High = $V_{DD} - 0.3 \text{ V}$ , G = +1 V/V,                           |  |  |

|                                             |                     |                    |                                  |             |       | V <sub>OUT</sub> = 0.1 V <sub>DD</sub> /2                                                      |  |  |

| Internal Hysteresis                         | V <sub>HYST</sub>   | _                  | 0.25                             | _           | V     |                                                                                                |  |  |

#### TABLE 1-4: TEMPERATURE SPECIFICATIONS

| Electrical Characteristics: Unless otherwise indicated, all limits are specified for: V <sub>DD</sub> = +1.8V to +5.5V, V <sub>SS</sub> = GND. |                |     |     |      |       |            |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----|-----|------|-------|------------|--|

| Parameters                                                                                                                                     | Sym            | Min | Тур | Max  | Units | Conditions |  |

| Temperature Ranges                                                                                                                             |                |     |     |      |       |            |  |

| Specified Temperature Range                                                                                                                    | T <sub>A</sub> | -40 | _   | +125 | °C    |            |  |

| Operating Temperature Range                                                                                                                    | T <sub>A</sub> | -40 | _   | +125 | °C    | (Note 1)   |  |

| Storage Temperature Range                                                                                                                      | T <sub>A</sub> | -65 | _   | +150 | °C    |            |  |

| Thermal Package Resistances                                                                                                                    |                |     |     |      |       |            |  |

| Thermal Resistance, 8L-2x3 TDFN                                                                                                                | $\theta_{JA}$  | _   | 41  | _    | °C/W  |            |  |

| Thermal Resistance, 8L-4x4 DFN                                                                                                                 | $\theta_{JA}$  | _   | 44  | _    | °C/W  | (Note 2)   |  |

| Thermal Resistance, 8L-SOIC                                                                                                                    | $\theta_{JA}$  | _   | 150 | _    | °C/W  |            |  |

$<sup>\</sup>textbf{Note} \quad \textbf{1:} \quad \text{Operation must not cause } T_J \text{ to exceed Maximum Junction Temperature specification (150°C)}.$

<sup>2:</sup> Measured on a standard JC51-7, four layer printed circuit board with ground plane and vias.

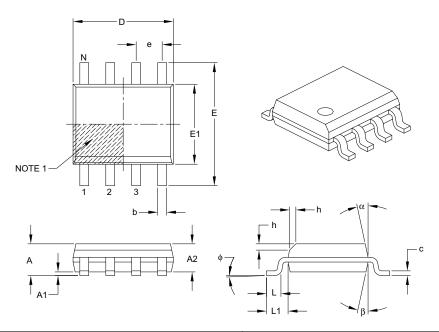

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

|                          | Units            | MILLIMETERS |          |      |

|--------------------------|------------------|-------------|----------|------|

|                          | Dimension Limits | MIN         | NOM      | MAX  |

| Number of Pins           | N                | 8           |          |      |

| Pitch                    | е                |             | 1.27 BSC |      |

| Overall Height           | A                | _           | _        | 1.75 |

| Molded Package Thickness | A2               | 1.25        | _        | -    |

| Standoff §               | A1               | 0.10        | _        | 0.25 |

| Overall Width            | E                | 6.00 BSC    |          |      |

| Molded Package Width     | E1               | 3.90 BSC    |          |      |

| Overall Length           | D                |             | 4.90 BSC |      |

| Chamfer (optional)       | h                | 0.25        | _        | 0.50 |

| Foot Length              | L                | 0.40        | _        | 1.27 |

| Footprint                | L1               | 1.04 REF    |          |      |

| Foot Angle               | ф                | 0°          | _        | 8°   |

| Lead Thickness           | С                | 0.17        | _        | 0.25 |

| Lead Width               | b                | 0.31        | _        | 0.51 |

| Mold Draft Angle Top     | α                | 5°          | _        | 15°  |

| Mold Draft Angle Bottom  | β                | 5°          | _        | 15°  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

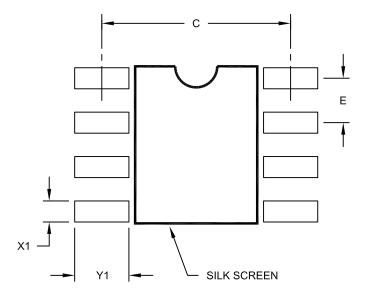

# 8-Lead Plastic Small Outline (SN) - Narrow, 3.90 mm Body [SOIC]

RECOMMENDED LAND PATTERN

|                         | Units            |  |          | MILLIMETERS |  |  |

|-------------------------|------------------|--|----------|-------------|--|--|

| Dimension               | Dimension Limits |  |          | MAX         |  |  |

| Contact Pitch           | Е                |  | 1.27 BSC |             |  |  |

| Contact Pad Spacing     | С                |  | 5.40     |             |  |  |

| Contact Pad Width (X8)  | X1               |  |          | 0.60        |  |  |

| Contact Pad Length (X8) | Y1               |  | ·        | 1.55        |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2057A

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

|                    | –X /XXX<br>perature Package<br>ange                                                                                                                                                                                                                                                 | a)<br>b)    | amples:  MCP6V01T-E/SN: Extended temperature, 8LD SOIC package.  MCP6V01-E/MNY:Extended temperature, 8LD 2x3 TDFN package.                                                                                                                        |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:            | MCP6V01 Single Op Amp MCP6V01T Single Op Amp (Tape and Reel for 2x3 TDFN andSOIC) MCP6V02 Dual Op Amp MCP6V02T Dual Op Amp (Tape and Reel for 4×4 DFN and SOIC) MCP6V03T Single Op Amp with Chip Select (Tape and Reel for SOIC)                                                    | a) b) a) b) | MCP6V02-E/MD: Extended temperature, 8LD 4x4 DFN package.  MCP6V02T-E/SN: Tape and Reel, Extended temperature, 8LD SOIC package.  MCP6V03-E/SN: Extended temperature, 8LD SOIC package.  MCP6V03-E/MNY:Extended temperature, 8LD 2x3 TDFN package. |

| Temperature Range: | E = -40°C to +125°C                                                                                                                                                                                                                                                                 |             |                                                                                                                                                                                                                                                   |

| Package:           | MD = Plastic Dual Flat, No-Lead (4×4x0.9 mm), 8-lead (MCP6V02 only)  MNY * = Plastic Dual Flat No Lead (2x3x0.75 mm), 8-lead (MCP6V01, MCP6V03)  SN = Plastic SOIC (150mil Body), 8-lead  * Y = nickel palladium gold manufacturing designator. Only available on the TDFN package. |             |                                                                                                                                                                                                                                                   |