TPA2010D1

SLOS417C-OCTOBER 2003-REVISED SEPTEMBER 2007

# 2.5-W MONO FILTER-FREE CLASS-D AUDIO POWER AMPLIFIER

## **FEATURES**

- Maximum Battery Life and Minimum Heat

- Efficiency With an 8-Ω Speaker:

- 88% at 400 mW

- 80% at 100 mW

- 2.8-mA Quiescent Current

- 0.5-µA Shutdown Current

- Only Three External Components

- Optimized PWM Output Stage Eliminates LC Output Filter

- Internally Generated 250-kHz Switching Frequency Eliminates Capacitor and Resistor

- Improved PSRR (–75 dB) and Wide Supply Voltage (2.5 V to 5.5 V) Eliminates Need for a Voltage Regulator

- Fully Differential Design Reduces RF Rectification and Eliminates Bypass Capacitor

- Improved CMRR Eliminates Two Input Coupling Capacitors

- Wafer Chip Scale Packaging (WCSP)

- NanoFree<sup>™</sup> Lead-Free (YZF)

- NanoStar™ SnPb (YEF)

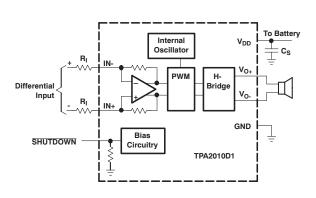

## **APPLICATION CIRCUIT**

## APPLICATIONS

- Wireless or Cellular Handsets and PDAs

- Personal Navigation Devices

- General Portable Audio Devices

- Linear Vibrator Drivers

## SEE ALSO

• TPA2032D1, TPA2033D1, TPA2034D1

## DESCRIPTION

The TPA2010D1 (sometimes referred to as TPA2010) is a 2.5-W high efficiency filter-free class-D audio power amplifier (class-D amp) in a 1,45 mm  $\times$  1,45 mm wafer chip scale package (WCSP) that requires only three external components.

Features like 88% efficiency, -75-dB PSRR, improved RF-rectification immunity, and 8 mm<sup>2</sup> total PCB area make the TPA2010D1 (TPA2010) class-D amp ideal for cellular handsets. A fast start-up time of 1 ms with minimal pop makes the TPA2010D1 (TPA2010) ideal for PDA applications.

In cellular handsets, the earpiece, speaker phone, and melody ringer can each be driven by the TPA2010D1. The TPA2010D1 allows independent gain while summing signals from seperate sources, and has a low 36  $\mu$ V noise floor, A-weighted.

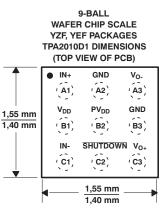

Note: Pin A1 is marked with a "0" for Pb-free (YZF) and a "1" for SnPb (YEF).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. NanoFree, NanoStar are trademarks of Texas Instruments.

## TPA2010D1

SLOS417C-OCTOBER 2003-REVISED SEPTEMBER 2007

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## **ORDERING INFORMATION**

| T <sub>A</sub>  | PACKAGE                                      | PART NUMBER                 | SYMBOL |

|-----------------|----------------------------------------------|-----------------------------|--------|

| –40°C to 85°C – | Wafer chip scale package (YEF)               | TPA2010D1YEF <sup>(1)</sup> | AJZ    |

|                 | Wafer chip scale packaging – Lead free (YZF) | TPA2010D1YZF <sup>(1)</sup> | AKO    |

(1) The YEF and YZF packages are only available taped and reeled. To order add the suffix *R* to the end of the part number for a reel of 3000, or add the suffix *T* to the end of the part number for a reel of 250 (e.g. TPA2010D1YEFR).

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted

|                  |                                                               |                              | TPA2010D1                         |  |

|------------------|---------------------------------------------------------------|------------------------------|-----------------------------------|--|

| v                | Supply veltage                                                | In active mode               |                                   |  |

| V <sub>DD</sub>  | Supply voltage                                                | In SHUTDOWN mode             | –0.3 V to 7 V                     |  |

| VI               | Input voltage                                                 |                              | –0.3 V to V <sub>DD</sub> + 0.3 V |  |

|                  | Continuous total power dissipation                            | See Dissipation Rating Table |                                   |  |

| T <sub>A</sub>   | Operating free-air temperature                                |                              | -40°C to 85°C                     |  |

| $T_{J}$          | Operating junction temperature                                |                              | –40°C to 150°C                    |  |

| T <sub>stg</sub> | Storage temperature                                           |                              | –65°C to 150°C                    |  |

|                  | Load temperature 1.6 mm (1/16 inch) from appendix 10 appendix | YZF                          | 260°C                             |  |

|                  | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds  | YEF                          | 235°C                             |  |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## **RECOMMENDED OPERATING CONDITIONS**

|                 |                                 |                                        | MIN | NOM MAX             | UNIT |

|-----------------|---------------------------------|----------------------------------------|-----|---------------------|------|

| $V_{DD}$        | Supply voltage                  |                                        | 2.5 | 5.5                 | V    |

| $V_{\text{IH}}$ | High-level input voltage        | SHUTDOWN                               | 1.3 | V <sub>DD</sub>     | V    |

| $V_{\text{IL}}$ | Low-level input voltage         | SHUTDOWN                               | 0   | 0.35                | V    |

| RI              | Input resistor                  | Gain ≤ 20 V/V (26 dB)                  | 15  |                     | kΩ   |

| VIC             | Common mode input voltage range | $V_{DD}$ = 2.5 V, 5.5 V, CMRR ≤ -49 dB | 0.5 | V <sub>DD</sub> 0.8 | V    |

| T <sub>A</sub>  | Operating free-air temperature  |                                        | -40 | 85                  | °C   |

## PACKAGE DISSIPATION RATINGS

| PACKAGE | DERATING FACTOR <sup>(1)</sup> | T <sub>A</sub> ≤ 25°C<br>POWER RATING | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|--------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|

| YEF     | 7.8 mW/°C                      | 780 mW                                | 429 mW                                | 312 mW                                |

| YZF     | 7.8 mW/°C                      | 780 mW                                | 429 mW                                | 312 mW                                |

(1) Derating factor measure with High K board.

## **ELECTRICAL CHARACTERISTICS**

$T_{\text{A}}$  = 25°C (unless otherwise noted)

|                     | PARAMETER                                          | TEST CONDITIONS                                                                                                                      | MIN                      | TYP                             | MAX                              | UNIT          |

|---------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------|----------------------------------|---------------|

| V <sub>OS</sub>     | Output offset voltage<br>(measured differentially) | $V_{I} = 0 \text{ V}, \text{ A}_{V} = 2 \text{ V/V}, \text{ V}_{DD} = 2.5 \text{ V} \text{ to } 5.5 \text{ V}$                       |                          | 1                               | 25                               | mV            |

| PSRR                | Power supply rejection ratio                       | V <sub>DD</sub> = 2.5 V to 5.5 V                                                                                                     |                          | -75                             | -55                              | dB            |

| CMRR                | Common mode rejection ratio                        | $V_{DD} = 2.5 \text{ V to } 5.5 \text{ V}, V_{IC} = V_{DD}/2 \text{ to } 0.5 \text{ V}, V_{IC} = V_{DD}/2 \text{ to } 0.5 \text{ V}$ |                          | -68                             | -49                              | dB            |

| I <sub>IH</sub>     | High-level input current                           | V <sub>DD</sub> = 5.5 V, V <sub>I</sub> = 5.8 V                                                                                      |                          |                                 | 100                              | μA            |

| $ I_{ L} $          | Low-level input current                            | $V_{DD} = 5.5 \text{ V}, \text{ V}_{I} = -0.3 \text{ V}$                                                                             |                          |                                 | 5                                | μA            |

|                     |                                                    | V <sub>DD</sub> = 5.5 V, no load                                                                                                     |                          | 3.4                             | 4.9                              |               |

| I <sub>(Q)</sub>    | Quiescent current                                  | V <sub>DD</sub> = 3.6 V, no load                                                                                                     |                          | 2.8                             |                                  | mA            |

|                     |                                                    | V <sub>DD</sub> = 2.5 V, no load                                                                                                     |                          | 2.2                             | 3.2                              |               |

| I <sub>(SD)</sub>   | Shutdown current                                   | $V_{(SHUTDOWN)} = 0.35 \text{ V}, V_{DD} = 2.5 \text{ V} \text{ to } 5.5 \text{ V}$                                                  |                          | 0.5                             | 2                                | μA            |

|                     |                                                    | V <sub>DD</sub> = 2.5 V                                                                                                              |                          | 700                             |                                  |               |

| r <sub>DS(on)</sub> | Static drain-source on-state<br>resistance         | V <sub>DD</sub> = 3.6 V                                                                                                              | 500                      |                                 |                                  | mΩ            |

|                     |                                                    | V <sub>DD</sub> = 5.5 V                                                                                                              |                          | 400                             |                                  |               |

|                     | Output impedance in SHUTDOWN                       | V <sub>(SHUTDOWN)</sub> = 0.35 V                                                                                                     |                          | >1                              |                                  | kΩ            |

| f <sub>(sw)</sub>   | Switching frequency                                | $V_{DD} = 2.5 \text{ V} \text{ to } 5.5 \text{ V}$                                                                                   | 200                      | 250                             | 300                              | kHz           |

|                     | Gain                                               | $V_{DD} = 2.5 V \text{ to } 5.5 V$                                                                                                   | 285 kΩ<br>R <sub>I</sub> | <u>300 kΩ</u><br>R <sub>I</sub> | $\frac{315  k\Omega}{R_{\rm I}}$ | $\frac{V}{V}$ |

|                     | Resistance from shutdown to GND                    |                                                                                                                                      |                          | 300                             |                                  | kΩ            |

## **OPERATING CHARACTERISTICS**

### $T_{A}$ = 25°C, Gain = 2 V/V, $R_{L}$ = 8 $\Omega$ (unless otherwise noted)

|                                     | PARAMETER                                            | TEST CONDITION                                                                                          | MIN TYF                                                                        | MAX     | UNIT |                   |  |

|-------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------|------|-------------------|--|

|                                     |                                                      |                                                                                                         | $V_{DD} = 5 V$                                                                 | 2.5     | ;    |                   |  |

|                                     |                                                      | THD + N = 10%, f = 1 kHz, $R_L$ = 4 $\Omega$                                                            | V <sub>DD</sub> = 3.6 V                                                        | 1.3     | 5    | W                 |  |

|                                     |                                                      |                                                                                                         | V <sub>DD</sub> = 2.5 V                                                        | 0.52    |      |                   |  |

|                                     |                                                      |                                                                                                         | $V_{DD} = 5 V$                                                                 | 2.08    | ;    |                   |  |

|                                     | THD + N = 1%, f = 1 kHz, R <sub>L</sub> = 4 $\Omega$ | V <sub>DD</sub> = 3.6 V                                                                                 | 1.06                                                                           | i       | W    |                   |  |

| р                                   |                                                      |                                                                                                         | V <sub>DD</sub> = 2.5 V                                                        | 0.42    |      |                   |  |

| Po                                  | Output power                                         |                                                                                                         | $V_{DD} = 5 V$                                                                 | 1.45    | ,    |                   |  |

|                                     | THD + N = 10%, f = 1 kHz, $R_L = 8 \Omega$           | V <sub>DD</sub> = 3.6 V                                                                                 | 0.73                                                                           | 5       | W    |                   |  |

|                                     |                                                      |                                                                                                         | V <sub>DD</sub> = 2.5 V                                                        | 0.33    | 5    |                   |  |

|                                     |                                                      |                                                                                                         | $V_{DD} = 5 V$                                                                 | 1.19    |      |                   |  |

|                                     |                                                      | THD + N = 1%, f = 1 kHz, $R_L = 8 \Omega$                                                               | V <sub>DD</sub> = 3.6 V                                                        | 0.59    |      | W                 |  |

|                                     |                                                      |                                                                                                         | V <sub>DD</sub> = 2.5 V                                                        | 0.26    | ;    |                   |  |

|                                     |                                                      | $V_{DD} = 5 \text{ V}, \text{ P}_{O} = 1 \text{ W}, \text{ R}_{L} = 8 \Omega, \text{ f} = 1 \text{ kH}$ | 0.18%                                                                          | )       |      |                   |  |

| THD+N                               | Total harmonic distortion plus<br>noise              | $V_{DD}$ = 3.6 V, $P_O$ = 0.5 W, $R_L$ = 8 $\Omega$ , f =                                               | 0.19%                                                                          | )       |      |                   |  |

|                                     |                                                      | $V_{DD}$ = 2.5 V, P <sub>O</sub> = 200 mW, R <sub>L</sub> = 8 Ω, f                                      | 0.20%                                                                          | )       |      |                   |  |

| k <sub>SVR</sub>                    | Supply ripple rejection ratio                        | $V_{DD}$ = 3.6 V, Inputs ac-grounded with C <sub>i</sub> = 2 µF                                         | $    f = 217 \text{ Hz}, \\ V_{(\text{RIPPLE})} = 200 \text{ mV}_{\text{pp}} $ | -67     | ,    | dB                |  |

| SNR                                 | Signal-to-noise ratio                                | $V_{DD}$ = 5 V, $P_O$ = 1 W, $R_L$ = 8 $\Omega$                                                         |                                                                                | 97      | ,    | dB                |  |

| V                                   |                                                      | V <sub>DD</sub> = 3.6 V, f = 20 Hz to 20 kHz,                                                           | No weighting                                                                   | 48      | 5    |                   |  |

| V <sub>n</sub> Output voltage noise | Oulput voltage holse                                 | Inputs ac-grounded with $C_i = 2 \ \mu F$                                                               | A weighting                                                                    | 36      | i    | μV <sub>RMS</sub> |  |

| CMRR                                | Common mode rejection ratio                          | $V_{DD}$ = 3.6 V, $V_{IC}$ = 1 $V_{pp}$                                                                 | f = 217 Hz                                                                     | -63     |      | dB                |  |

| ZI                                  | Input impedance                                      |                                                                                                         |                                                                                | 142 150 | 158  | kΩ                |  |

|                                     | Start-up time from shutdown                          | V <sub>DD</sub> = 3.6 V                                                                                 |                                                                                | 1       |      | ms                |  |

Copyright © 2003–2007, Texas Instruments Incorporated

### **Terminal Functions**

| TERMIN          | TERMINAL |     | DESCRIPTION                          |  |  |  |

|-----------------|----------|-----|--------------------------------------|--|--|--|

| NAME            | YEF, YZF | I/O | DESCRIPTION                          |  |  |  |

| IN–             | C1       | I   | Negative differential input          |  |  |  |

| IN+             | A1       | I   | Positive differential input          |  |  |  |

| V <sub>DD</sub> | B1       | Ι   | Power supply                         |  |  |  |

| V <sub>O+</sub> | C3       | 0   | Positive BTL output                  |  |  |  |

| GND             | A2, B3   | I   | High-current ground                  |  |  |  |

| V <sub>O-</sub> | A3       | 0   | Negative BTL output                  |  |  |  |

| SHUTDOWN        | C2       | I   | Shutdown terminal (active low logic) |  |  |  |

| PVDD            | B2       | I   | Power supply                         |  |  |  |

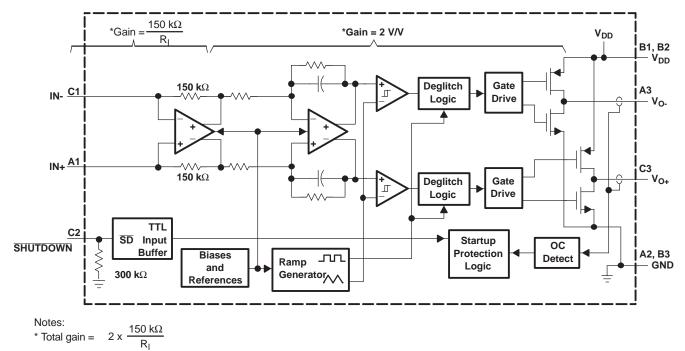

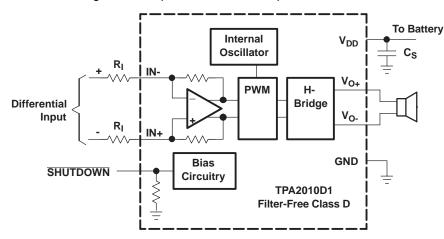

## FUNCTIONAL BLOCK DIAGRAM

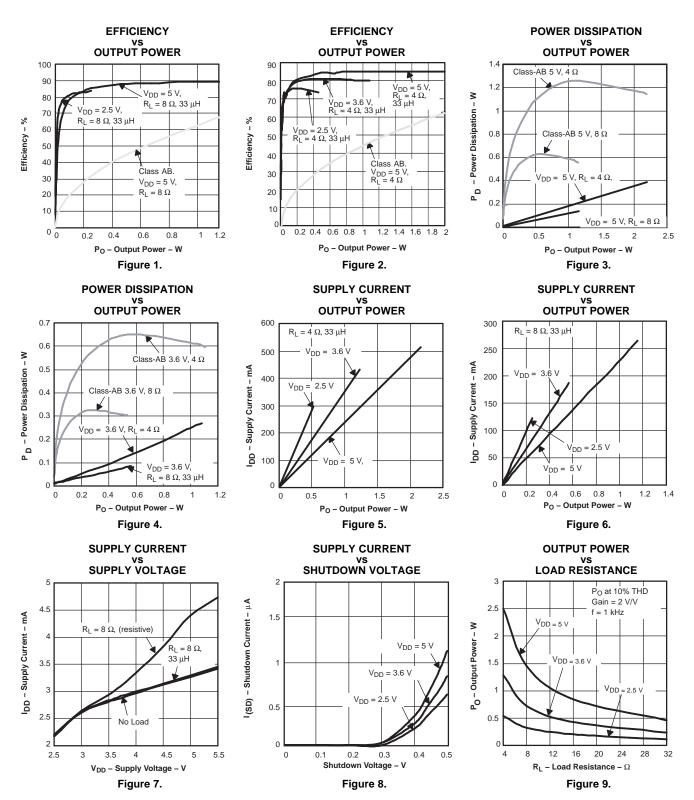

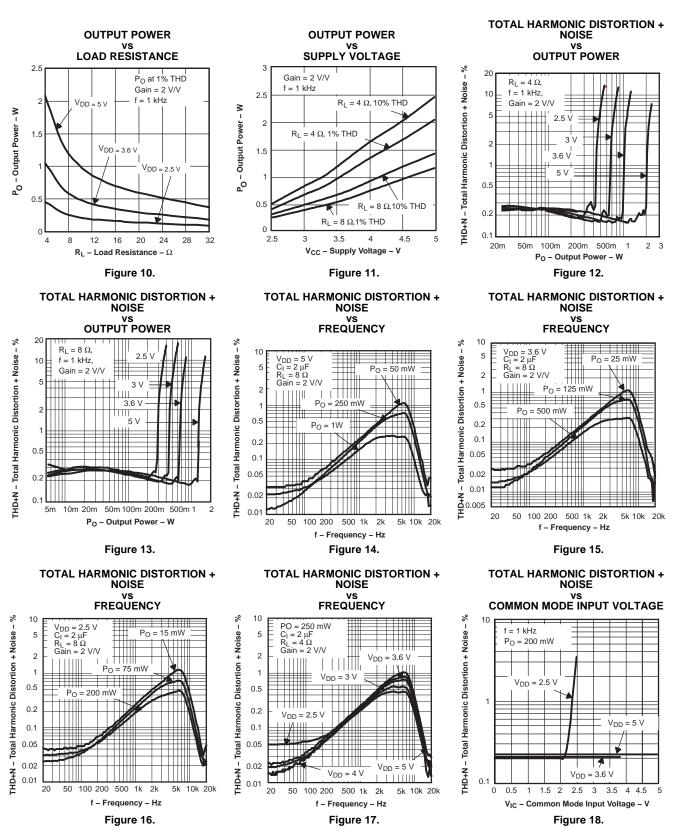

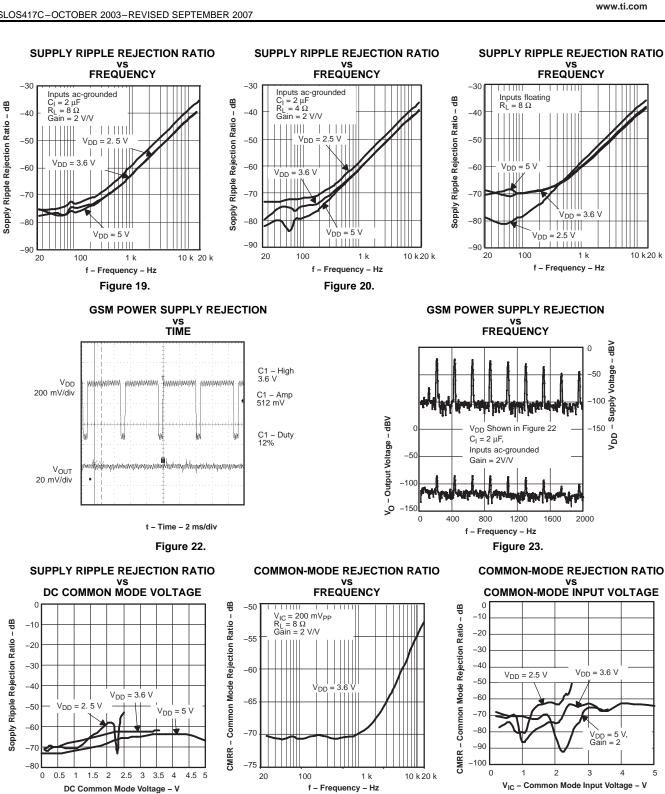

## **TYPICAL CHARACTERISTICS**

### **TABLE OF GRAPHS**

|                             |                                      |                              | FIGURE         |

|-----------------------------|--------------------------------------|------------------------------|----------------|

|                             | Efficiency                           | vs Output power              | 1, 2           |

| PD                          | Power dissipation                    | vs Output power              | 3, 4           |

|                             | Supply current                       | vs Output power              | 5, 6           |

| I <sub>(Q)</sub>            | Quiescent current                    | vs Supply voltage            | 7              |

| I <sub>(SD)</sub>           | Shutdown current                     | vs Shutdown voltage          | 8              |

|                             |                                      | vs Supply voltage            | 9              |

| P <sub>O</sub> Output power | Output power                         | vs Load resistance           | 10, 11         |

|                             |                                      | vs Output power              | 12, 13         |

| THD+N                       | Total harmonic distortion plus noise | vs Frequency                 | 14, 15, 16, 17 |

|                             |                                      | vs Common-mode input voltage | 18             |

| K <sub>SVR</sub>            | Supply voltage rejection ratio       | vs Frequency                 | 19, 20, 21     |

|                             |                                      | vs Time                      | 22             |

| GSM power supply rejection  | GSIM power supply rejection          | vs Frequency                 | 23             |

| K <sub>SVR</sub>            | Supply voltage rejection ratio       | vs Common-mode input voltage | 24             |

|                             | Common mode seis stien setie         | vs Frequency                 | 25             |

| CMRR                        | Common-mode rejection ratio          | vs Common-mode input voltage | 26             |

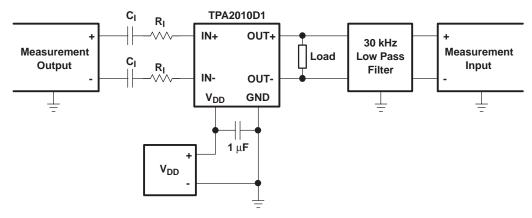

### **TEST SET-UP FOR GRAPHS**

Notes:

(1) CI was Shorted for any Common-Mode input voltage measurement

(2) A 33-µH inductor was placed in series with the load resistor to emulate a small speaker for efficiency measurements.

(3) The 30-kHz low-pass filter is required even if the analyzer has an internal low-pass filter. An RC low pass filter (100 Ω, 47 nF) is used on each output for the data sheet graphs.

IEXAS RUMENTS

Figure 24.

Figure 25.

## **APPLICATION INFORMATION**

### FULLY DIFFERENTIAL AMPLIFIER

The TPA2010D1 is a fully differential amplifier with differential inputs and outputs. The fully differential amplifier consists of a differential amplifier and a common-mode amplifier. The differential amplifier ensures that the amplifier outputs a differential voltage on the output that is equal to the differential input times the gain. The common-mode feedback ensures that the common-mode voltage at the output is biased around  $V_{DD}/2$  regardless of the common-mode voltage at the input. The fully differential TPA2010D1 can still be used with a single-ended input; however, the TPA2010D1 should be used with differential inputs when in a noisy environment, like a wireless handset, to ensure maximum noise rejection.

### Advantages of Fully Differential Amplifiers

- Input-coupling capacitors not required:

- The fully differential amplifier allows the inputs to be biased at voltage other than mid-supply. For example, if a codec has a midsupply lower than the midsupply of the TPA2010D1, the common-mode feedback circuit will adjust, and the TPA2010D1 outputs will still be biased at midsupply of the TPA2010D1. The inputs of the TPA2010D1 can be biased from 0.5 V to V<sub>DD</sub> –0.8 V. If the inputs are biased outside of that range, input-coupling capacitors are required.

- Midsupply bypass capacitor, C<sub>(BYPASS)</sub>, not required:

- The fully differential amplifier does not require a bypass capacitor. This is because any shift in the midsupply affects both positive and negative channels equally and cancels at the differential output.

- Better RF-immunity:

- GSM handsets save power by turning on and shutting off the RF transmitter at a rate of 217 Hz. The transmitted signal is picked-up on input and output traces. The fully differential amplifier cancels the signal much better than the typical audio amplifier.

### **COMPONENT SELECTION**

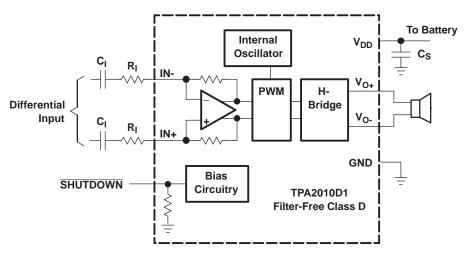

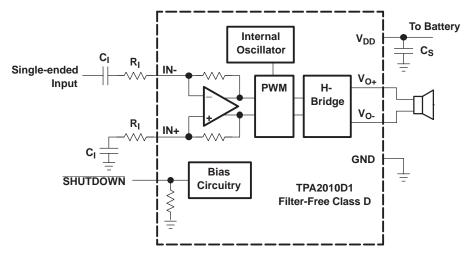

Figure 27 shows the TPA2010D1 typical schematic with differential inputs and Figure 28 shows the TPA2010D1 with differential inputs and input capacitors, and Figure 29 shows the TPA2010D1 with single-ended inputs. Differential inputs should be used whenever possible because the single-ended inputs are much more susceptible to noise.

| REF DES                       | VALUE             | EIA SIZE | MANUFACTURER | PART NUMBER    |

|-------------------------------|-------------------|----------|--------------|----------------|

| RI                            | 150 kΩ (±0.5%)    | 0402     | Panasonic    | ERJ2RHD154V    |

| C <sub>S</sub>                | 1 µF (+22%, –80%) | 0402     | Murata       | GRP155F50J105Z |

| C <sub>I</sub> <sup>(1)</sup> | 3.3 nF (±10%)     | 0201     | Murata       | GRP033B10J332K |

### **Table 1. Typical Component Values**

(1)  $C_l$  is only needed for single-ended input or if  $V_{ICM}$  is not between 0.5 V and  $V_{DD} - 0.8$  V.  $C_l = 3.3$  nF (with  $R_l = 150 \text{ k}\Omega$ ) gives a high-pass corner frequency of 321 Hz.

### Input Resistors (R<sub>I</sub>)

The input resistors  $(R_1)$  set the gain of the amplifier according to Equation 1.

Gain =

$$\frac{2 \times 150 \text{ k}\Omega}{\text{R}_{\text{I}}}$$

$\left(\frac{\text{V}}{\text{V}}\right)$

(1)

Resistor matching is very important in fully differential amplifiers. The balance of the output on the reference voltage depends on matched ratios of the resistors. CMRR, PSRR, and cancellation of the second harmonic distortion diminish if resistor mismatch occurs. Therefore, it is recommended to use 1% tolerance resistors or better to keep the performance optimized. Matching is more important than overall tolerance. Resistor arrays with 1% matching can be used with a tolerance greater than 1%.

Place the input resistors very close to the TPA2010D1 to limit noise injection on the high-impedance nodes.

For optimal performance the gain should be set to 2 V/V or lower. Lower gain allows the TPA2010D1 to operate at its best, and keeps a high voltage at the input making the inputs less susceptible to noise.

### Decoupling Capacitor (C<sub>S</sub>)

The TPA2010D1 is a high-performance class-D audio amplifier that requires adequate power supply decoupling to ensure the efficiency is high and total harmonic distortion (THD) is low. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically 1  $\mu$ F, placed as close as possible to the device V<sub>DD</sub> lead works best. Placing this decoupling capacitor close to the TPA2010D1 is very important for the efficiency of the class-D amplifier, because any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency. For filtering lower-frequency noise signals, a 10  $\mu$ F or greater capacitor placed near the audio power amplifier would also help, but it is not required in most applications because of the high PSRR of this device.

### Input Capacitors (C<sub>I</sub>)

The TPA2010D1 does not require input coupling capacitors if the design uses a differential source that is biased from 0.5 V to  $V_{DD}$  –0.8 V (shown in Figure 27). If the input signal is not biased within the recommended common-mode input range, if needing to use the input as a high pass filter (shown in Figure 28), or if using a single-ended source (shown in Figure 29), input coupling capacitors are required.

The input capacitors and input resistors form a high-pass filter with the corner frequency,  $f_c$ , determined in Equation 2.

$$f_{C} = \frac{1}{\left(2\pi R_{I}C_{I}\right)}$$

(2)

The value of the input capacitor is important to consider as it directly affects the bass (low frequency) performance of the circuit. Speakers in wireless phones cannot usually respond well to low frequencies, so the corner frequency can be set to block low frequencies in this application.

Equation 3 is reconfigured to solve for the input coupling capacitance.

$$C_{||} = \frac{1}{\left(2\pi R_{||} f_{c}\right)}$$

(3)

If the corner frequency is within the audio band, the capacitors should have a tolerance of 10% or better, because any mismatch in capacitance causes an impedance mismatch at the corner frequency and below.

For a flat low-frequency response, use large input coupling capacitors (1  $\mu$ F). However, in a GSM phone the ground signal is fluctuating at 217 Hz, but the signal from the codec does not have the same 217 Hz fluctuation. The difference between the two signals is amplified, sent to the speaker, and heard as a 217 Hz hum.

Figure 28. TPA2010D1 Application Schematic With Differential Input and Input Capacitors

Figure 29. TPA2010D1 Application Schematic With Single-Ended Input

### SUMMING INPUT SIGNALS WITH THE TPA2010D1

Most wireless phones or PDAs need to sum signals at the audio power amplifier or just have two signal sources that need separate gain. The TPA2010D1 makes it easy to sum signals or use separate signal sources with different gains. Many phones now use the same speaker for the earpiece and ringer, where the wireless phone would require a much lower gain for the phone earpiece than for the ringer. PDAs and phones that have stereo headphones require summing of the right and left channels to output the stereo signal to the mono speaker.

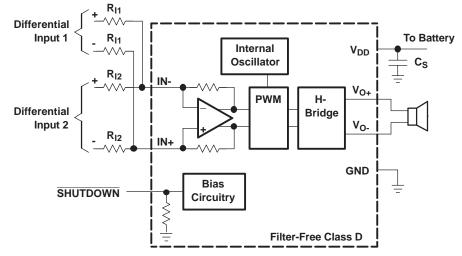

### **Summing Two Differential Input Signals**

Two extra resistors are needed for summing differential signals (a total of 5 components). The gain for each input source can be set independently (see Equation 4 and Equation 5, and Figure 30).

$$Gain 1 = \frac{V_O}{V_{I1}} = \frac{2 \times 150 \text{ k}\Omega}{R_{I1}} \quad \begin{pmatrix} V \\ V \end{pmatrix}$$

(4)

$$Gain 2 = \frac{V_O}{V_{I2}} = \frac{2 \times 150 \text{ k}\Omega}{R_{I2}} \quad \begin{pmatrix} V \\ V \end{pmatrix}$$

(5)

If summing left and right inputs with a gain of 1 V/V, use  $R_{I1} = R_{I2} = 300 \text{ k}\Omega$ .

## TPA2010D1

SLOS417C-OCTOBER 2003-REVISED SEPTEMBER 2007

If summing a ring tone and a phone signal, set the ring-tone gain to Gain 2 = 2 V/V, and the phone gain to gain 1 = 0.1 V/V. The resistor values would be. . .

$$R_{11} = 3 M\Omega$$

, and  $= R_{12} = 150 k\Omega$ .

Figure 30. Application Schematic With TPA2010D1 Summing Two Differential Inputs

### Summing a Differential Input Signal and a Single-Ended Input Signal

Figure 31 shows how to sum a differential input signal and a single-ended input signal. Ground noise can couple in through IN+ with this method. It is better to use differential inputs. The corner frequency of the single-ended input is set by  $C_{12}$ , shown in Equation 8. To assure that each input is balanced, the single-ended input must be driven by a low-impedance source even if the input is not in use

$$Gain 1 = \frac{V_O}{V_{11}} = \frac{2 \times 150 \text{ k}\Omega}{R_{11}} \quad \left(\frac{V}{V}\right)$$

$$Gain 2 = \frac{V_O}{V_{11}} = \frac{2 \times 150 \text{ k}\Omega}{R_{11}} \quad \left(\frac{V}{V}\right)$$

(6)

$$C_{12} = \frac{1}{(1-1)^{12}}$$

(V) (7)

$$S_{12} = \frac{12}{(2\pi R_{12} f_{c2})}$$

(8)

If summing a ring tone and a phone signal, the phone signal should use a differential input signal while the ring tone might be limited to a single-ended signal. Phone gain is set at gain 1 = 0.1 V/V, and the ring-tone gain is set to gain 2 = 2 V/V, the resistor values would be...

$R_{11} = 3 M\Omega$ , and  $= R_{12} = 150 k\Omega$ .

The high pass corner frequency of the single-ended input is set by  $C_{12}$ . If the desired corner frequency is less than 20 Hz...

$$C_{12} > \frac{1}{(2\pi 150k\Omega 20Hz)}$$

(9)

$$C_{12} > 53 nF$$

(10)

$$Differential Input 1

Single-Ended Input 2

$$R_{11} \\ C_{12} \\ R_{12} \\ R$$$$

Figure 31. Application Schematic With TPA2010D1 Summing Differential Input and Single-Ended Input Signals

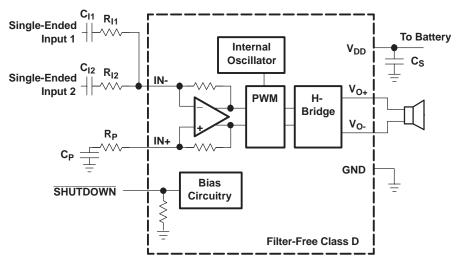

### Summing Two Single-Ended Input Signals

Four resistors and three capacitors are needed for summing single-ended input signals. The gain and corner frequencies ( $f_{c1}$  and  $f_{c2}$ ) for each input source can be set independently (see Equation 11 through Equation 14, and Figure 32). Resistor,  $R_P$ , and capacitor,  $C_P$ , are needed on the IN+ terminal to match the impedance on the IN– terminal. The single-ended inputs must be driven by low impedance sources even if one of the inputs is not outputting an ac signal.

Gain 1 =

$$\frac{V_0}{V_{11}} = \frac{2 \times 150 \text{ k}\Omega}{R_{11}}$$

$\left(\frac{V}{V}\right)$  (11)

$$Gain 2 = \frac{\sqrt{O}}{V_{I2}} = \frac{2 \times 150 \text{ k}\Omega}{R_{I2}} \quad \left(\frac{V}{V}\right)$$

(12)

$$C_{|1} = \frac{1}{\left(2\pi R_{|1} f_{c1}\right)}$$

(13)

$$C_{I2} = \frac{1}{\left(2\pi R_{I2} f_{c2}\right)}$$

$$C_{D} = C_{I4} + C_{I2}$$

(14)

(15)

$$R_{P} = \frac{R_{I1} \times R_{I2}}{(R_{P} - R_{I1})}$$

(15)

$$\begin{pmatrix} \mathsf{R}_{11} + \mathsf{R}_{12} \end{pmatrix} \tag{16}$$

Copyright © 2003–2007, Texas Instruments Incorporated

Figure 32. Application Schematic With TPA2010D1 Summing Two Single-Ended Inputs

## **BOARD LAYOUT**

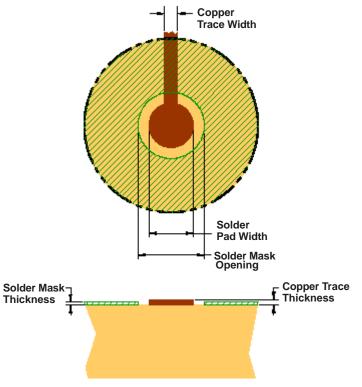

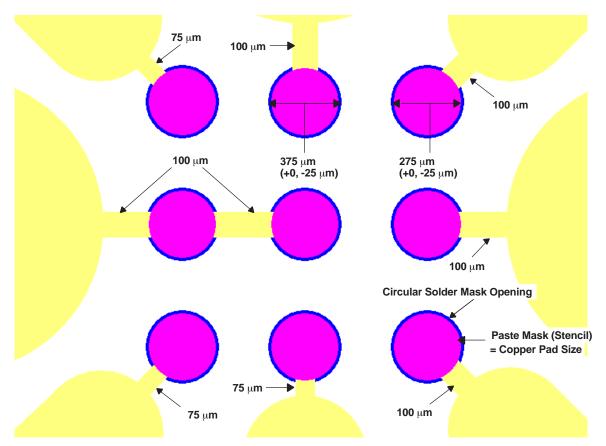

In making the pad size for the WCSP balls, it is recommended that the layout use nonsolder mask defined (NSMD) land. With this method, the solder mask opening is made larger than the desired land area, and the opening size is defined by the copper pad width. Figure 33 and Table 2 show the appropriate diameters for a WCSP layout. The TPA2010D1 evaluation module (EVM) layout is shown in the next section as a layout example.

Figure 33. Land Pattern Dimensions

### Table 2. Land Pattern Dimensions

| SOLDER PAD                    | COPPER PAD               | SOLDER MASK              | COPPER           | STENCIL                                  | STENCIL      |

|-------------------------------|--------------------------|--------------------------|------------------|------------------------------------------|--------------|

| DEFINITIONS                   |                          | OPENING                  | THICKNESS        | OPENING                                  | THICKNESS    |

| Nonsolder mask defined (NSMD) | 275 μm<br>(+0.0, –25 μm) | 375 μm<br>(+0.0, –25 μm) | 1 oz max (32 µm) | 275 μm x 275 μm Sq.<br>(rounded corners) | 125 µm thick |

### NOTES:

- 1. Circuit traces from NSMD defined PWB lands should be 75 μm to 100 μm wide in the exposed area inside the solder mask opening. Wider trace widths reduce device stand off and impact reliability.

- 2. Recommend solder paste is Type 3 or Type 4.

- 3. Best reilability results are achieved when the PWB laminate glass transition temperature is above the operating the range of the intended application.

- 4. For a PWB using a Ni/Au surface finish, the gold thickness should be less 0.5 μm to avoid a reduction in thermal fatigue performance.

- 5. Solder mask thickness should be less than 20 µm on top of the copper circuit pattern.

- 6. Best solder stencil preformance is achieved using laser cut stencils with electro polishing. Use of chemically etched stencils results in inferior solder paste volume control.

- 7. Trace routing away from WCSP device should be balanced in X and Y directions to avoid unintentional component movement due to solder wetting forces.

#### **Component Location**

Place all the external components very close to the TPA2010D1. The input resistors need to be very close to the TPA2010D1 input pins so noise does not couple on the high impedance nodes between the input resistors and the input amplifier of the TPA2010D1. Placing the decoupling capacitor, CS, close to the TPA2010D1 is important for the efficiency of the class-D amplifier. Any resistance or inductance in the trace between the device and the capacitor can cause a loss in efficiency.

### Trace Width

Recommended trace width at the solder balls is 75 µm to 100 µm to prevent solder wicking onto wider PCB traces. Figure 34 shows the layout of the TPA2010D1 evaluation module (EVM).

For high current pins ( $V_{DD}$ , GND  $V_{O+}$ , and  $V_{O-}$ ) of the TPA2010D1, use 100-µm trace widths at the solder balls and at least 500-µm PCB traces to ensure proper performance and output power for the device.

For input pins (IN–, IN+, and SHUTDOWN) of the TPA2010D1, use 75- $\mu$ m to 100- $\mu$ m trace widths at the solder balls. IN– and IN+ pins need to run side-by-side to maximize common-mode noise cancellation. Placing input resistors, R<sub>IN</sub>, as close to the TPA2010D1 as possible is recommended.

Figure 34. Close Up of TPA2010D1 Land Pattern From TPA2010D1 EVM

## **EFFICIENCY AND THERMAL INFORMATION**

The maximum ambient temperature depends on the heat-sinking ability of the PCB system. The derating factor for the YEF and YEZ packages are shown in the dissipation rating table. Converting this to  $\theta_{JA}$ :

$$\theta_{\text{JA}} = \frac{1}{\text{Derating Factor}} = \frac{1}{0.0078} = 128.2^{\circ}\text{C/W}$$

(17)

Given  $\theta_{JA}$  of 128.2°C/W, the maximum allowable junction temperature of 150°C, and the maximum internal dissipation of 0.4 W (2.25 W, 4- $\Omega$  load, 5-V supply, from Figure 3), the maximum ambient temperature can be calculated with the following equation.

$$T_A Max = T_J Max - \theta_{JA} P_{Dmax} = 150 - 128.2 (0.4) = 98.72^{\circ}C$$

(18)

Equation 18 shows that the calculated maximum ambient temperature is  $98.72^{\circ}C$  at maximum power dissipation with a 5-V supply and 4- $\Omega$  a load, see Figure 3. The TPA2010D1 is designed with thermal protection that turns the device off when the junction temperature surpasses  $165^{\circ}C \sim 190^{\circ}C$  to prevent damage to the IC. Also, using speakers more resistive than 4- $\Omega$  dramatically increases the thermal performance by reducing the output current and increasing the efficiency of the amplifier.

## ELIMINATING THE OUTPUT FILTER WITH THE TPA2010D1

This section focuses on why the user can eliminate the output filter with the TPA2010D1.

### Effect on Audio

The class-D amplifier outputs a pulse-width modulated (PWM) square wave, which is the sum of the switching waveform and the amplified input audio signal. The human ear acts as a band-pass filter such that only the frequencies between approximately 20 Hz and 20 kHz are passed. The switching frequency components are much greater than 20 kHz, so the only signal heard is the amplified input audio signal.

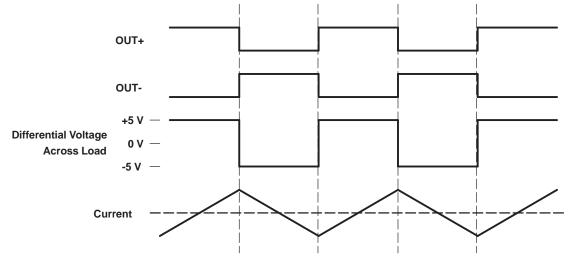

### Traditional Class-D Modulation Scheme

The traditional class-D modulation scheme, which is used in the TPA005Dxx family, has a differential output where each output is 180 degrees out of phase and changes from ground to the supply voltage,  $V_{DD}$ . Therefore, the differential pre-filtered output varies between positive and negative  $V_{DD}$ , where filtered 50% duty cycle yields 0 volts across the load. The traditional class-D modulation scheme with voltage and current waveforms is shown in Figure 35. Note that even at an average of 0 volts across the load (50% duty cycle), the current to the load is high causing a high loss and thus causing a high supply current.

Figure 35. Traditional Class-D Modulation Scheme's Output Voltage and Current Waveforms Into an Inductive Load With no Input

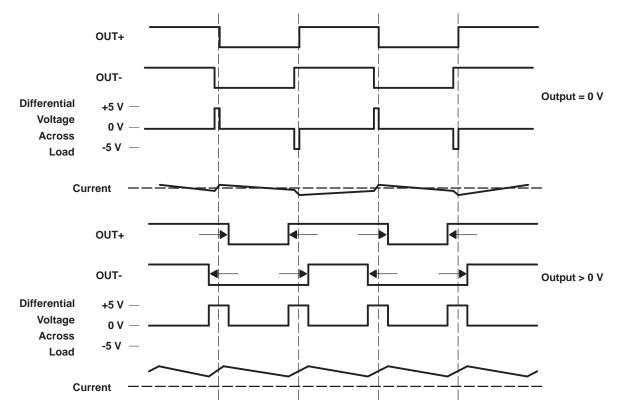

### **TPA2010D1 Modulation Scheme**

The TPA2010D1 uses a modulation scheme that still has each output switching from 0 to the supply voltage. However, OUT+ and OUT- are now in phase with each other with no input. The duty cycle of OUT+ is greater than 50% and OUT- is less than 50% for positive voltages. The duty cycle of OUT+ is less than 50% and OUT- is greater than 50% for negative voltages. The voltage across the load sits at 0 volts throughout most of the switching period greatly reducing the switching current, which reduces any I<sup>2</sup>R losses in the load.

## TPA2010D1

SLOS417C-OCTOBER 2003-REVISED SEPTEMBER 2007

Figure 36. The TPA2010D1 Output Voltage and Current Waveforms Into an Inductive Load

### Efficiency: Why You Must Use a Filter With the Traditional Class-D Modulation Scheme

The main reason that the traditional class-D amplifier needs an output filter is that the switching waveform results in maximum current flow. This causes more loss in the load, which causes lower efficiency. The ripple current is large for the traditional modulation scheme because the ripple current is proportional to voltage multiplied by the time at that voltage. The differential voltage swing is  $2 \times V_{DD}$  and the time at each voltage is half the period for the traditional modulation scheme. An ideal LC filter is needed to store the ripple current from each half cycle for the next half cycle, while any resistance causes power dissipation. The speaker is both resistive and reactive, whereas an LC filter is almost purely reactive.

The TPA2010D1 modulation scheme has very little loss in the load without a filter because the pulses are very short and the change in voltage is  $V_{DD}$  instead of  $2 \times V_{DD}$ . As the output power increases, the pulses widen making the ripple current larger. Ripple current could be filtered with an LC filter for increased efficiency, but for most applications the filter is not needed.

An LC filter with a cutoff frequency less than the class-D switching frequency allows the switching current to flow through the filter instead of the load. The filter has less resistance than the speaker that results in less power dissipated, which increases efficiency.

### Effects of Applying a Square Wave Into a Speaker

If the amplitude of a square wave is high enough and the frequency of the square wave is within the bandwidth of the speaker, a square wave could cause the voice coil to jump out of the air gap and/or scar the voice coil. A 250-kHz switching frequency, however, is not significant because the speaker cone movement is proportional to  $1/t^2$  for frequencies beyond the audio band. Therefore, the amount of cone movement at the switching frequency is very small. However, damage could occur to the speaker if the voice coil is not designed to handle the additional power. To size the speaker for added power, the ripple current dissipated in the load needs to be calculated by subtracting the theoretical supplied power, P<sub>SUP THEORETICAL</sub>, from the actual supply power, P<sub>SUP</sub>, at maximum output power, P<sub>OUT</sub>. The switching power dissipated in the speaker is the inverse of the measured efficiency,  $\eta_{MEASURED}$ , minus the theoretical efficiency,  $\eta_{THEORETICAL}$ .

$${}^{P}SPKR = {}^{P}SUP {}^{-P}SUP {}^{T}HEORETICAL {(at max output power)}$$

(19)

$$P_{SPKR} = \frac{P_{SUP}}{P_{OUT}} - \frac{P_{SUP THEORETICAL}}{P_{OUT}}$$

(at max output power) (20)

$$P_{SPKR} = P_{OUT} \left( \frac{1}{\eta_{MEASURED}} - \frac{1}{\eta_{THEORETICAL}} \right) (at max output power)$$

(21)

$$\eta \text{THEORETICAL} = \frac{\mathsf{R}_{L}}{\mathsf{R}_{L} + 2\mathsf{r}_{\mathsf{DS}(\mathsf{on})}} \text{ (at max output power)}$$

(22)

The maximum efficiency of the TPA2010D1 with a 3.6 V supply and an 8- $\Omega$  load is 86% from Equation 22. Using equation Equation 21 with the efficiency at maximum power (84%), we see that there is an additional 17 mW dissipated in the speaker. The added power dissipated in the speaker is not an issue as long as it is taken into account when choosing the speaker.

### When to Use an Output Filter

Design the TPA2010D1 without an output filter if the traces from amplifier to speaker are short. The TPA2010D1 passed FCC and CE radiated emissions with no shielding with speaker trace wires 100 mm long or less. Wireless handsets and PDAs are great applications for class-D without a filter.

A ferrite bead filter can often be used if the design is failing radiated emissions without an LC filter, and the frequency sensitive circuit is greater than 1 MHz. This is good for circuits that just have to pass FCC and CE because FCC and CE only test radiated emissions greater than 30 MHz. If choosing a ferrite bead, choose one with high impedance at high frequencies, but very low impedance at low frequencies.

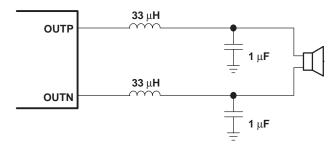

Use an LC output filter if there are low frequency (< 1 MHz) EMI sensitive circuits and/or there are long leads from amplifier to speaker.

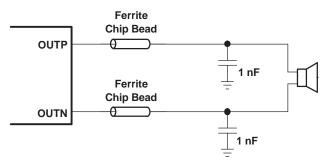

Figure 37 and Figure 38 show typical ferrite bead and LC output filters.

### Figure 37. Typical Ferrite Chip Bead Filter (Chip bead example: NEC/Tokin: N2012ZPS121)

Figure 38. Typical LC Output Filter, Cutoff Frequency of 27 kHz

www.ti.com

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TPA2010D1YEFR    | NRND                  | DSBGA        | YEF                | 9    |             | TBD                        | Call TI              | Call TI                      |                             |

| TPA2010D1YEFT    | NRND                  | DSBGA        | YEF                | 9    |             | TBD                        | Call TI              | Call TI                      |                             |

| TPA2010D1YZFR    | ACTIVE                | DSBGA        | YZF                | 9    | 3000        | Green (RoHS<br>& no Sb/Br) | SNAGCU               | Level-1-260C-UNLIM           |                             |

| TPA2010D1YZFT    | ACTIVE                | DSBGA        | YZF                | 9    | 250         | Green (RoHS<br>& no Sb/Br) | SNAGCU               | Level-1-260C-UNLIM           |                             |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

## PACKAGE MATERIALS INFORMATION

www.ti.com

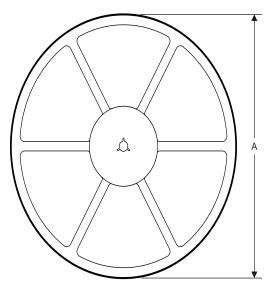

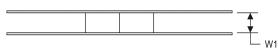

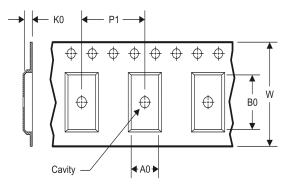

## TAPE AND REEL INFORMATION

### REEL DIMENSIONS

TEXAS INSTRUMENTS

### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

| TAPE AND REEL INFORMATION |  |

|---------------------------|--|

|                           |  |

| Device        | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPA2010D1YZFR | DSBGA           | YZF                | 9 | 3000 | 180.0                    | 8.4                      | 1.65       | 1.65       | 0.81       | 4.0        | 8.0       | Q1               |

| TPA2010D1YZFR | DSBGA           | YZF                | 9 | 3000 | 180.0                    | 8.4                      | 1.65       | 1.65       | 0.81       | 4.0        | 8.0       | Q1               |

| TPA2010D1YZFT | DSBGA           | YZF                | 9 | 250  | 180.0                    | 8.4                      | 1.65       | 1.65       | 0.81       | 4.0        | 8.0       | Q1               |

| TPA2010D1YZFT | DSBGA           | YZF                | 9 | 250  | 180.0                    | 8.4                      | 1.65       | 1.65       | 0.81       | 4.0        | 8.0       | Q1               |

TEXAS INSTRUMENTS

www.ti.com

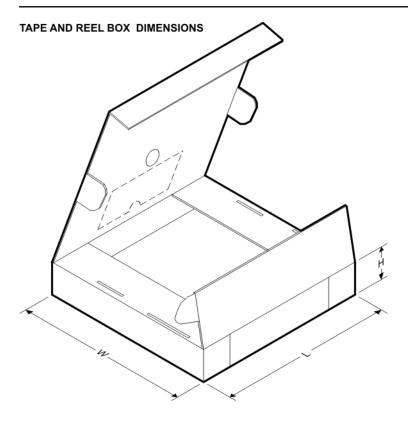

# PACKAGE MATERIALS INFORMATION

10-Oct-2011

\*All dimensions are nominal

| Device        | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPA2010D1YZFR | DSBGA        | YZF             | 9    | 3000 | 210.0       | 185.0      | 35.0        |

| TPA2010D1YZFR | DSBGA        | YZF             | 9    | 3000 | 220.0       | 220.0      | 34.0        |

| TPA2010D1YZFT | DSBGA        | YZF             | 9    | 250  | 210.0       | 185.0      | 35.0        |

| TPA2010D1YZFT | DSBGA        | YZF             | 9    | 250  | 220.0       | 220.0      | 34.0        |

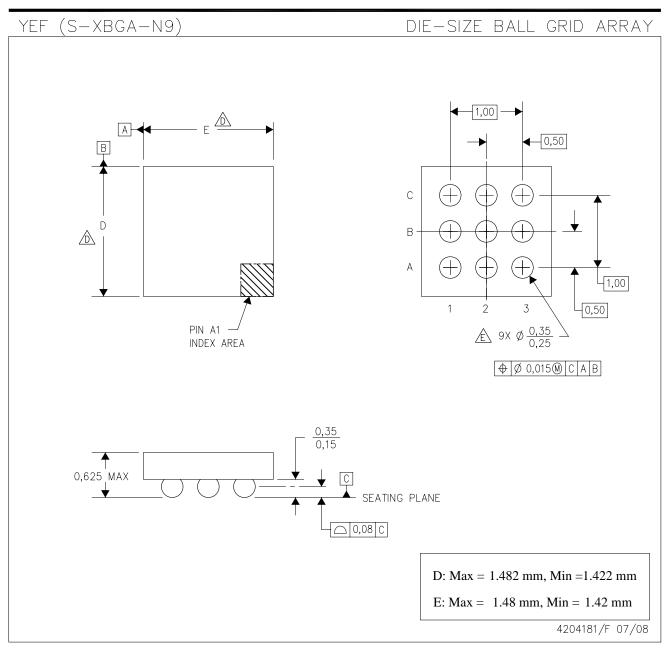

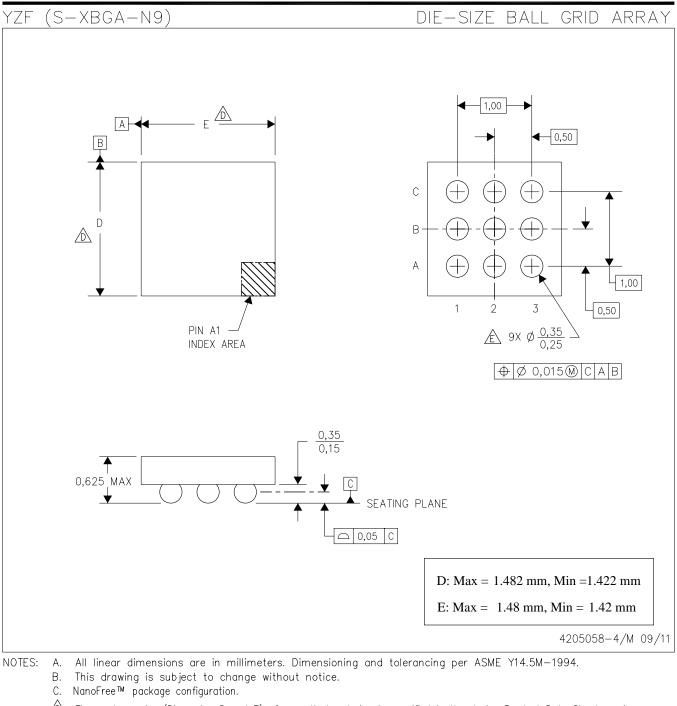

- NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. NanoStar™ package configuration.

- Devices in YEF package can have dimension D ranging from 1.44 to 2.15 mm and dimension E ranging from 1.44 to 2.15 mm. To determine the exact package size of a particular device, refer to the device datasheet or contact a local TI representative.

- E. Reference Product Data Sheet for array population.  $3 \times 3$  matrix pattern is shown for illustration only.

- F. This package contains tin-lead (SnPb) balls. Refer to YZF (Drawing #4205058) for lead-free balls.

NanoStar is a trademark of Texas Instruments.

## **MECHANICAL DATA**

The package size (Dimension D and E) of a particular device is specified in the device Product Data Sheet version of this drawing, in case it cannot be found in the product data sheet please contact a local TI representative.

🖄 Reference Product Data Sheet for array population.

3 x 3 matrix pattern is shown for illustration only. F. This package contains Pb-free balls.

Refer to YEF (Drawing #4204181) for tin-lead (SnPb) balls.

NanoFree is a trademark of Texas Instruments.

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated