SDAS083C - APRIL 1982 - REVISED MARCH 2002

- Eight Latches in a Single Package

- 3-State Bus-Driving True Outputs

• Full Parallel Access for Loading

- Buffered Control Inputs

- pnp Inputs Reduce dc Loading on Data Lines

### description

These octal transparent D-type latches feature 3-state outputs designed specifically for driving highly capacitive or relatively low-impedance loads. They are particularly suitable for implementing buffer registers, I/O ports, bidirectional bus drivers, and working registers.

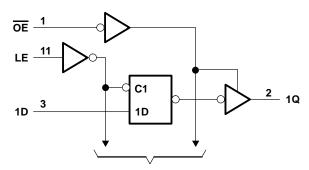

While the latch-enable (LE) input is high, the Q outputs follow the data (D) inputs. When LE is taken low, the Q outputs are latched at the logic levels set up at the D inputs.

A buffered output-enable ( $\overline{OE}$ ) input can be used to place the eight outputs in either a normal logic state (high or low) or a high-impedance state. In the high-impedance state, the outputs neither load nor drive the bus lines significantly. The high-impedance state and the increased drive provide the capability to drive bus lines without interface or pullup components.

$\overline{\text{OE}}$  does not affect internal operations of the latches. Old data can be retained or new data can be entered while the outputs are off.

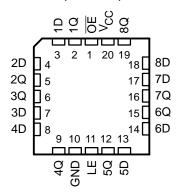

| SN54ALS373A, J OR W PACKAGE                 |

|---------------------------------------------|

| SN54AS373 J PACKAGE                         |

| SN74ALS373A, SN74AS373 DW, N, OR NS PACKAGE |

| (TOP VIEW)                                  |

| OE  |              | U | 20 | ] v <sub>cc</sub> |

|-----|--------------|---|----|-------------------|

| 1Q  | 2            |   | 19 | ] 8Q              |

| 1D  | <b>[</b> ] 3 |   | 18 | ] 8D              |

| 2D  | 4            |   | 17 | ] 7D              |

| 2Q  | <b>[</b> 5   |   | 16 | ] 7Q              |

| 3Q  | 6            |   | 15 | ] 6Q              |

| 3D  | [7           |   | 14 | ] 6D              |

| 4D  | 8 ]          |   | 13 | ] 5D              |

| 4Q  | <b>[</b> 9   |   | 12 | ] 5Q              |

| GND | [ 10         |   | 11 | ] LE              |

|     |              |   |    |                   |

#### SN54ALS373A, SN54AS373...FK PACKAGE (TOP VIEW)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2002, Texas Instruments Incorporated On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

SDAS083C – APRIL 1982 – REVISED MARCH 2002

| TA             | PAC          | PACKAGE <sup>†</sup> ORDERABLE<br>PART NUMBER |                | TOP-SIDE<br>MARKING |  |  |  |  |

|----------------|--------------|-----------------------------------------------|----------------|---------------------|--|--|--|--|

|                | PDIP – N     | Tube                                          | SN74ALS373AN   | SN74ALS373AN        |  |  |  |  |

|                | PDIP – N     | Pdbe                                          | SN74AS373N     | SN74AS373N          |  |  |  |  |

|                |              | Tube                                          | SN74ALS373ADW  | ALS373A             |  |  |  |  |

| 0°C to 70°C    | °C SOIC – DW | Tape and reel                                 | SN74ALS373ADWR | ALSSTSA             |  |  |  |  |

|                |              | Tube                                          | SN74AS373DW    | 46272               |  |  |  |  |

|                |              | Tape and reel                                 | SN74AS373DWR   | AS373               |  |  |  |  |

|                | 005 10       | Topo and roal                                 | SN74ALS373ANSR | ALS373A             |  |  |  |  |

|                | SOP – NS     | Tape and reel                                 | SN74AS373NSR   | 74AS373             |  |  |  |  |

|                | CDIP – J     | Tube                                          | SNJ54ALS373AJ  | SNJ54ALS373AJ       |  |  |  |  |

|                | CDIP – J     | PdbP                                          | SNJ54AS373J    | SNJ54AS373J         |  |  |  |  |

| –55°C to 125°C | CFP – W      | Tube                                          | SNJ54ALS373AW  | SNJ54ALS373AW       |  |  |  |  |

|                |              | Taba                                          | SNJ54ALS373AFK | SNJ54ALS373AFK      |  |  |  |  |

|                | LCCC – FK    | Tube                                          | SNJ54AS373FK   | SNJ54AS373FK        |  |  |  |  |

#### **ORDERING INFORMATION**

<sup>†</sup> Package drawings, standard packing quantities, thermal data, symbolization, and PCB design guidelines are available at www.ti.com/sc/package.

| FUNCTION TABLE |

|----------------|

| (each latch)   |

|    | INPUTS | OUTPUT |                |

|----|--------|--------|----------------|

| OE | LE     | D      | Q              |

| L  | Н      | Н      | Н              |

| L  | Н      | L      | L              |

| L  | L      | Х      | Q <sub>0</sub> |

| н  | Х      | Х      | Z              |

# logic diagram (positive logic)

**To Seven Other Channels**

SDAS083C - APRIL 1982 - REVISED MARCH 2002

# absolute maximum ratings over operating free-air temperature range (SN54ALS373A, SN74ALS373A) (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub>                                |            |

|----------------------------------------------------------------|------------|

| Input voltage, V <sub>1</sub>                                  |            |

| Package thermal impedance, $\theta_{IA}$ (see Note 1): DW pack |            |

|                                                                | e 69°C/W   |

| NS packa                                                       | age 60°C/W |

| Storage temperature range, T <sub>stg</sub>                    |            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: The package thermal impedance is calculated in accordance with JESD 51-7.

#### recommended operating conditions

|                |                                | SN5 | 54ALS37 | '3A | SN74ALS373A |     |      | UNIT |

|----------------|--------------------------------|-----|---------|-----|-------------|-----|------|------|

|                |                                | MIN | NOM     | MAX | MIN         | NOM | MAX  | UNIT |

| VCC            | Supply voltage                 | 4.5 | 5       | 5.5 | 4.5         | 5   | 5.5  | V    |

| VIH            | High-level input voltage       | 2   |         |     | 2           |     |      | V    |

| VIL            | Low-level input voltage        |     |         | 0.7 |             |     | 0.8  | V    |

| ЮН             | High-level output current      |     |         | -1  |             |     | -2.6 | mA   |

| IOL            | Low-level output current       |     |         | 12  |             |     | 24   | mA   |

| Т <sub>А</sub> | Operating free-air temperature | -55 |         | 125 | 0           |     | 70   | °C   |

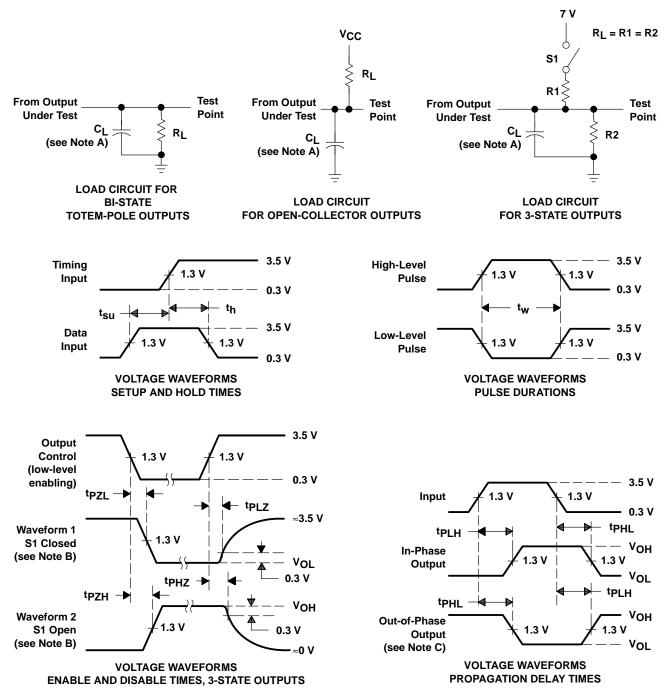

# timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figure 1)

|                 |                                         | SN54ALS373A<br>MIN MAX |  | SN74AL | UNIT |      |

|-----------------|-----------------------------------------|------------------------|--|--------|------|------|

|                 |                                         |                        |  | MIN    | MAX  | UNIT |

| fclock          | Clock frequency                         |                        |  |        |      | MHz  |

| tw              | Pulse duration, LE high                 | 12                     |  | 10     |      | ns   |

| t <sub>su</sub> | Setup time, data before LE $\downarrow$ | 10                     |  | 10     |      | ns   |

| t <sub>h</sub>  | Hold time, data after LE $\downarrow$   | 7                      |  | 7      |      | ns   |

SDAS083C - APRIL 1982 - REVISED MARCH 2002

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED        | TERTO                             | TEST CONDITIONS           |                    | 4ALS37 | '3A  | SN7                |      |      |      |

|------------------|-----------------------------------|---------------------------|--------------------|--------|------|--------------------|------|------|------|

| PARAMETER        | TEST C                            | UNDITIONS                 | MIN                | түр†   | MAX  | MIN                | түр† | MAX  | UNIT |

| VIK              | V <sub>CC</sub> = 4.5 V,          | lj = -18 mA               |                    |        | -1.5 |                    |      | -1.5 | V    |

|                  | V <sub>CC</sub> = 4.5 V to 5.5 V, | I <sub>OH</sub> = -0.4 mA | V <sub>CC</sub> –2 |        |      | V <sub>CC</sub> –2 |      |      |      |

| VOH              | $\lambda = -45\lambda$            | I <sub>OH</sub> = -1 mA   | 2.4                | 3.3    |      |                    |      |      | V    |

|                  | $V_{CC} = 4.5 V$                  | I <sub>OH</sub> = -2.6 mA |                    |        |      | 2.4                | 3.2  |      |      |

| N/               |                                   | I <sub>OL</sub> = 12 mA   |                    | 0.25   | 0.4  |                    | 0.25 | 0.4  | V    |

| VOL              | $V_{CC} = 4.5 V$                  | I <sub>OL</sub> = 24 mA   |                    |        |      |                    | 0.35 | 0.5  | v    |

| lozh             | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.7 V    |                    |        | 20   |                    |      | 20   | μA   |

| I <sub>OZL</sub> | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 0.4 V    |                    |        | -20  |                    |      | -20  | μA   |

| lj               | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 7 V      |                    |        | 0.1  |                    |      | 0.1  | mA   |

| Iн               | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 2.7 V    |                    |        | 20   |                    |      | 20   | μA   |

| ١ <sub>١L</sub>  | V <sub>CC</sub> = 5.5 V,          | V <sub>I</sub> = 0.4 V    |                    |        | -0.1 |                    |      | -0.1 | mA   |

| IO‡              | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.25 V   | -20                |        | -112 | -30                |      | -112 | mA   |

|                  |                                   | Outputs high              |                    | 9      | 16   |                    | 9    | 16   |      |

| ICC              | $V_{CC} = 5.5 V$                  | Outputs low               |                    | 16     | 25   |                    | 16   | 25   | mA   |

|                  |                                   | Outputs disabled          |                    | 17     | 27   |                    | 17   | 27   |      |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one-half of the true short-circuit output current, IOS.

### switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | то<br>(оитрит) | Cl<br>R1<br>R2 | _ = 50 pl<br>l = 500 | 2,          | ,   | UNIT |

|------------------|-----------------|----------------|----------------|----------------------|-------------|-----|------|

|                  |                 | SN54AL         |                | S373A                | SN74ALS373A |     |      |

|                  |                 |                | MIN            | MAX                  | MIN         | MAX |      |

| <sup>t</sup> PLH | D               |                | 2              | 17                   | 2           | 12  | ns   |

| <sup>t</sup> PHL |                 | Q              | 1              | 19                   | 4           | 16  | 115  |

| <sup>t</sup> PLH |                 | 4              | 6              | 29                   | 6           | 22  | ns   |

| <sup>t</sup> PHL | LE              | Any Q          | 1              | 27                   | 7           | 23  | 115  |

| <sup>t</sup> PZH |                 |                | 6              | 22                   | 1           | 18  |      |

| <sup>t</sup> PZL | OE              | Any Q          | 5              | 24                   | 5           | 20  | ns   |

| <sup>t</sup> PHZ | ŌĒ              | Apy O          | 2              | 16                   | 1           | 10  |      |

| <sup>t</sup> PLZ | UE              | Any Q          | 2              | 24                   | 2           | 12  | ns   |

§ For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

SDAS083C - APRIL 1982 - REVISED MARCH 2002

# absolute maximum ratings over operating free-air temperature range (SN54AS373, SN74AS373) (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub><br>Input voltage, V <sub>I</sub> |            |                |

|------------------------------------------------------------------|------------|----------------|

| Voltage applied to any output in the high state of               |            |                |

| Package thermal impedance, $\theta_{JA}$ (see Note 1):           | DW package | 58°C/W         |

|                                                                  | N package  | 69°C/W         |

|                                                                  | NS package | 60°C/W         |

| Storage temperature range, T <sub>stg</sub>                      | ·          | –65°C to 150°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 2: The package thermal impedance is calculated in accordance with JESD 51-7.

#### recommended operating conditions

|                |                                | SN54AS373 SN74AS373 |     |     | /3  | UNIT |     |      |

|----------------|--------------------------------|---------------------|-----|-----|-----|------|-----|------|

|                |                                | MIN                 | NOM | MAX | MIN | NOM  | MAX | UNIT |

| VCC            | Supply voltage                 | 4.5                 | 5   | 5.5 | 4.5 | 5    | 5.5 | V    |

| VIH            | High-level input voltage       | 2                   |     |     | 2   |      |     | V    |

| VIL            | Low-level input voltage        |                     |     | 0.8 |     |      | 0.8 | V    |

| ЮН             | High-level output current      |                     |     | -12 |     |      | -15 | mA   |

| IOL            | Low-level output current       |                     |     | 32  |     |      | 48  | mA   |

| Т <sub>А</sub> | Operating free-air temperature | -55                 |     | 125 | 0   |      | 70  | °C   |

# timing requirements over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted) (see Figure 1)

|                 |                                         | SN54A | S373 | SN74A | UNIT |      |

|-----------------|-----------------------------------------|-------|------|-------|------|------|

|                 |                                         | MIN   | MAX  | MIN   | MAX  | UNIT |

| fclock          | Clock frequency                         |       |      |       |      | MHz  |

| tw              | Pulse duration, LE high                 | 5.5*  |      | 4.5*  |      | ns   |

| t <sub>su</sub> | Setup time, data before LE $\downarrow$ | 2*    |      | 2*    |      | ns   |

| t <sub>h</sub>  | Hold time, data after LE $\downarrow$   | 3*    |      | 3*    |      | ns   |

\* On products compliant to MIL-STD-883, Class B, this parameter is based on characterization data but is not production tested.

SDAS083C - APRIL 1982 - REVISED MARCH 2002

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| DADAMETED       | TEST CONDITIONS                   |                          |                    | 154AS37 | '3   | SN                 | 3     | UNIT |    |

|-----------------|-----------------------------------|--------------------------|--------------------|---------|------|--------------------|-------|------|----|

| PARAMETER       | TEST C                            | MIN                      | түр†               | MAX     | MIN  | TYP†               | MAX   | UNIT |    |

| VIK             | V <sub>CC</sub> = 4.5 V,          | lı = –18 mA              |                    |         | -1.2 |                    |       | -1.2 | V  |

|                 | V <sub>CC</sub> = 4.5 V to 5.5 V, | $I_{OH} = -2 \text{ mA}$ | V <sub>CC</sub> –2 |         |      | V <sub>CC</sub> –2 |       |      |    |

| VOH             |                                   | I <sub>OH</sub> = -12 mA | 2.4                | 3.2     |      |                    |       |      | V  |

|                 | $V_{CC} = 4.5 V$                  | I <sub>OH</sub> = -15 mA |                    |         |      | 2.4                | 3.3   |      |    |

| Ve              | $\lambda = 45 \lambda$            | I <sub>OL</sub> = 32 mA  |                    | 0.27    | 0.5  |                    |       |      | V  |

| VOL             | $V_{CC} = 4.5 V$                  | I <sub>OL</sub> = 48 mA  |                    |         |      |                    | 0.32  | 0.5  | v  |

| IOZH            | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.7 V   |                    |         | 50   |                    |       | 50   | μA |

| IOZL            | $V_{CC} = 5.5 V,$                 | V <sub>O</sub> = 0.4 V   |                    |         | -50  |                    |       | -50  | μA |

| lj              | $V_{CC} = 5.5 V,$                 | $V_{I} = 7 V$            |                    |         | 0.1  |                    |       | 0.1  | mA |

| Ιн              | V <sub>CC</sub> = 5.5 V,          | VI = 2.7 V               |                    |         | 20   |                    |       | 20   | μA |

| ١ <sub>١L</sub> | V <sub>CC</sub> = 5.5 V,          | VI = 0.4 V               |                    | -0.02   | -0.5 |                    | -0.02 | -0.5 | mA |

| 10‡             | V <sub>CC</sub> = 5.5 V,          | V <sub>O</sub> = 2.25 V  | -30                |         | -112 | -30                |       | -112 | mA |

|                 |                                   | Outputs high             |                    | 55      | 90   |                    | 55    | 90   |    |

| ICC             | $V_{CC} = 5.5 V$                  | Outputs low              |                    | 55      | 85   |                    | 55    | 85   | mA |

|                 |                                   | Outputs disabled         |                    | 65      | 100  |                    | 65    | 100  |    |

<sup>†</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

<sup>‡</sup> The output conditions have been chosen to produce a current that closely approximates one-half of the true short-circuit output current, IOS.

### switching characteristics (see Figure 1)

| PARAMETER        | FROM<br>(INPUT) | TO<br>(OUTPUT) | Ci<br>R <sup>2</sup><br>R2 | CC = 4.5<br>L = 50 pF<br>1 = 500 Ω<br>2 = 500 Ω<br>A = MIN t | <u>2,</u><br>2, | 3    | UNIT |

|------------------|-----------------|----------------|----------------------------|--------------------------------------------------------------|-----------------|------|------|

|                  |                 |                | SN54A                      | S373                                                         | SN74AS373       |      |      |

|                  |                 |                | MIN                        | MAX                                                          | MIN             | MAX  |      |

| <sup>t</sup> PLH | D               |                | 3                          | 9                                                            | 3.5             | 6    | ns   |

| <sup>t</sup> PHL | U               | Q              | 3                          | 8                                                            | 3.5             | 6    | 115  |

| <sup>t</sup> PLH | LE              | 10             | 6.5                        | 14.5                                                         | 6.5             | 11.5 | 20   |

| <sup>t</sup> PHL | LC              | Any Q          | 5                          | 9                                                            | 5               | 7.5  | ns   |

| <sup>t</sup> PZH |                 | 10             | 2                          | 7.5                                                          | 2               | 6.5  |      |

| <sup>t</sup> PZL | OE              | Any Q          | 4.5                        | 10.5                                                         | 4.5             | 9.5  | ns   |

| <sup>t</sup> PHZ | ŌĒ              | Am/ 0          | 3                          | 10                                                           | 3               | 6.5  |      |

| <sup>t</sup> PLZ | UE              | Any Q          | 3                          | 8                                                            | 3               | 7    | ns   |

§ For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

SN54ALS373A, SN54AS373, SN74ALS373A, SN74AS373 OCTAL TRANSPARENT D-TYPE LATCHES

WITH 3-STATE OUTPUTS

SDAS083C - APRIL 1982 - REVISED MARCH 2002

#### PARAMETER MEASUREMENT INFORMATION SERIES 54ALS/74ALS AND 54AS/74AS DEVICES

NOTES: A. CL includes probe and jig capacitance.

- B. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

C. When measuring propagation delay items of 3-state outputs, switch S1 is open.

- D. All input pulses have the following characteristics: PRR  $\leq$  1 MHz, t<sub>r</sub> = t<sub>f</sub> = 2 ns, duty cycle = 50%.

- D. All input pulses have the following characteristics. FRR  $\leq 1$  with  $z_i$ ,  $t_i = t_i = 2$  hs, duty cycle =

- E. The outputs are measured one at a time with one transition per measurement.

10-Jun-2014

# PACKAGING INFORMATION

| Orderable Device |               | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan                   | Lead/Ball Finish  | MSL Peak Temp             | Op Temp (°C) | Device Marking                           | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|----------------------------|-------------------|---------------------------|--------------|------------------------------------------|---------|

| 83020012A        | (1)<br>ACTIVE | LCCC         | FK                 | 20   | 1              | (2)<br>TBD                 | (6)<br>POST-PLATE | (3)<br>N / A for Pkg Type | -55 to 125   | (4/5)<br>83020012A<br>SNJ54ALS<br>373AFK | Samples |

| 8302001RA        | ACTIVE        | CDIP         | J                  | 20   | 1              | TBD                        | A42               | N / A for Pkg Type        | -55 to 125   | 8302001RA<br>SNJ54ALS373AJ               | Samples |

| 8302001SA        | ACTIVE        | CFP          | W                  | 20   | 1              | TBD                        | A42               | N / A for Pkg Type        | -55 to 125   | 8302001SA<br>SNJ54ALS373AW               | Samples |

| JM38510/37203B2A | ACTIVE        | LCCC         | FK                 | 20   | 1              | TBD                        | POST-PLATE        | N / A for Pkg Type        | -55 to 125   | JM38510/<br>37203B2A                     | Samples |

| JM38510/37203BRA | ACTIVE        | CDIP         | J                  | 20   | 1              | TBD                        | A42               | N / A for Pkg Type        | -55 to 125   | JM38510/<br>37203BRA                     | Samples |

| M38510/37203B2A  | ACTIVE        | LCCC         | FK                 | 20   | 1              | TBD                        | POST-PLATE        | N / A for Pkg Type        | -55 to 125   | JM38510/<br>37203B2A                     | Samples |

| M38510/37203BRA  | ACTIVE        | CDIP         | J                  | 20   | 1              | TBD                        | A42               | N / A for Pkg Type        | -55 to 125   | JM38510/<br>37203BRA                     | Samples |

| SN54ALS373AJ     | ACTIVE        | CDIP         | J                  | 20   | 1              | TBD                        | A42               | N / A for Pkg Type        | -55 to 125   | SN54ALS373AJ                             | Samples |

| SN54AS373J       | ACTIVE        | CDIP         | J                  | 20   | 1              | TBD                        | A42               | N / A for Pkg Type        | -55 to 125   | SN54AS373J                               | Samples |

| SN74ALS373ADBLE  | OBSOLETE      | SSOP         | DB                 | 20   |                | TBD                        | Call TI           | Call TI                   | 0 to 70      |                                          |         |

| SN74ALS373ADBR   | ACTIVE        | SSOP         | DB                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU         | Level-1-260C-UNLIM        | 0 to 70      | G373A                                    | Samples |

| SN74ALS373ADW    | ACTIVE        | SOIC         | DW                 | 20   | 25             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU         | Level-1-260C-UNLIM        | 0 to 70      | ALS373A                                  | Samples |

| SN74ALS373ADWG4  | ACTIVE        | SOIC         | DW                 | 20   | 25             | Green (RoHS<br>& no Sb/Br) | CU NIPDAU         | Level-1-260C-UNLIM        | 0 to 70      | ALS373A                                  | Samples |

| SN74ALS373ADWR   | ACTIVE        | SOIC         | DW                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU         | Level-1-260C-UNLIM        | 0 to 70      | ALS373A                                  | Samples |

| SN74ALS373ADWRG4 | ACTIVE        | SOIC         | DW                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU         | Level-1-260C-UNLIM        | 0 to 70      | ALS373A                                  | Samples |

| SN74ALS373AN     | ACTIVE        | PDIP         | N                  | 20   | 20             | Pb-Free<br>(RoHS)          | CU NIPDAU         | N / A for Pkg Type        | 0 to 70      | SN74ALS373AN                             | Samples |

| SN74ALS373AN3    | OBSOLETE      | PDIP         | N                  | 20   |                | TBD                        | Call TI           | Call TI                   | 0 to 70      |                                          |         |

| SN74ALS373ANSR   | ACTIVE        | SO           | NS                 | 20   | 2000           | Green (RoHS<br>& no Sb/Br) | CU NIPDAU         | Level-1-260C-UNLIM        | 0 to 70      | ALS373A                                  | Samples |

# PACKAGE OPTION ADDENDUM

10-Jun-2014

| Orderable Device | Status   | Package Type |         | Pins |      | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Device Marking                  | Samples |

|------------------|----------|--------------|---------|------|------|----------------------------|------------------|--------------------|--------------|---------------------------------|---------|

|                  | (1)      |              | Drawing |      | Qty  | (2)                        | (6)              | (3)                |              | (4/5)                           |         |

| SN74ALS373ANSRG4 | ACTIVE   | SO           | NS      | 20   | 2000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | ALS373A                         | Samples |

| SN74AS373DW      | ACTIVE   | SOIC         | DW      | 20   | 25   | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | AS373                           | Samples |

| SN74AS373DWR     | OBSOLETE | SOIC         | DW      | 20   |      | TBD                        | Call TI          | Call TI            | 0 to 70      | AS373                           |         |

| SN74AS373DWRE4   | OBSOLETE | SOIC         | DW      | 20   |      | TBD                        | Call TI          | Call TI            | 0 to 70      |                                 |         |

| SN74AS373DWRG4   | OBSOLETE | SOIC         | DW      | 20   |      | TBD                        | Call TI          | Call TI            | 0 to 70      |                                 |         |

| SN74AS373N       | ACTIVE   | PDIP         | Ν       | 20   | 20   | Pb-Free<br>(RoHS)          | CU NIPDAU        | N / A for Pkg Type | 0 to 70      | SN74AS373N                      | Samples |

| SN74AS373N3      | OBSOLETE | PDIP         | N       | 20   |      | TBD                        | Call TI          | Call TI            | 0 to 70      |                                 |         |

| SN74AS373NSR     | ACTIVE   | SO           | NS      | 20   | 2000 | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-1-260C-UNLIM | 0 to 70      | 74AS373                         | Samples |

| SNJ54ALS373AFK   | ACTIVE   | LCCC         | FK      | 20   | 1    | TBD                        | POST-PLATE       | N / A for Pkg Type | -55 to 125   | 83020012A<br>SNJ54ALS<br>373AFK | Samples |

| SNJ54ALS373AJ    | ACTIVE   | CDIP         | J       | 20   | 1    | TBD                        | A42              | N / A for Pkg Type | -55 to 125   | 8302001RA<br>SNJ54ALS373AJ      | Samples |

| SNJ54ALS373AW    | ACTIVE   | CFP          | W       | 20   | 1    | TBD                        | A42              | N / A for Pkg Type | -55 to 125   | 8302001SA<br>SNJ54ALS373AW      | Samples |

| SNJ54AS373FK     | ACTIVE   | LCCC         | FK      | 20   | 1    | TBD                        | POST-PLATE       | N / A for Pkg Type | -55 to 125   | SNJ54AS<br>373FK                | Samples |

| SNJ54AS373J      | ACTIVE   | CDIP         | J       | 20   | 1    | TBD                        | A42              | N / A for Pkg Type | -55 to 125   | SNJ54AS373J                     | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

# PACKAGE OPTION ADDENDUM

10-Jun-2014

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF SN54ALS373A, SN54AS373, SN74ALS373A, SN74AS373 :

- Catalog: SN74ALS373A, SN74AS373

- Military: SN54ALS373A, SN54AS373

NOTE: Qualified Version Definitions:

- Catalog TI's standard catalog product

- Military QML certified for Military and Defense Applications

# PACKAGE MATERIALS INFORMATION

www.ti.com

Pin1

Quadrant

Q1

Q1

Q1

Q1

**P1**

(mm)

12.0

12.0

12.0

12.0

w

(mm)

16.0

24.0

24.0

24.0

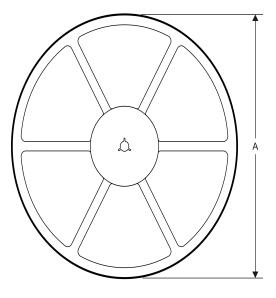

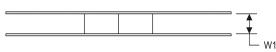

### TAPE AND REEL INFORMATION

#### REEL DIMENSIONS

TEXAS INSTRUMENTS

SO

SO

NS

NS

TAPE AND REEL INFORMATION

SN74ALS373ANSR

SN74AS373NSR

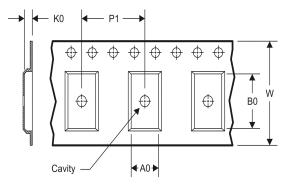

#### TAPE DIMENSIONS

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

| All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |

|----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|

| Device                     | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) |

| SN74ALS373ADBR             | SSOP            | DB                 | 20 | 2000 | 330.0                    | 16.4                     | 8.2        | 7.5        | 2.5        |

| SN74ALS373ADWR             | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.0       | 2.7        |

20

20

2000

2000

330.0

330.0

24.4

24.4

8.2

8.2

13.0

13.0

2.5

2.5

TEXAS INSTRUMENTS

www.ti.com

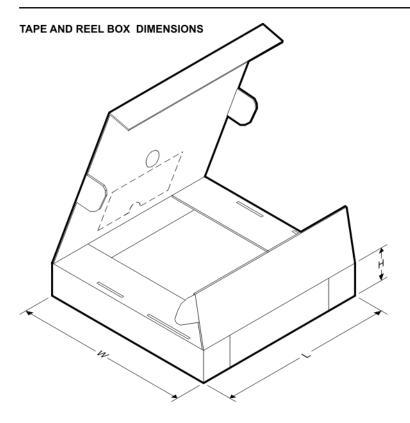

# PACKAGE MATERIALS INFORMATION

17-Aug-2012

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN74ALS373ADBR | SSOP         | DB              | 20   | 2000 | 367.0       | 367.0      | 38.0        |

| SN74ALS373ADWR | SOIC         | DW              | 20   | 2000 | 367.0       | 367.0      | 45.0        |

| SN74ALS373ANSR | SO           | NS              | 20   | 2000 | 367.0       | 367.0      | 45.0        |

| SN74AS373NSR   | SO           | NS              | 20   | 2000 | 367.0       | 367.0      | 45.0        |

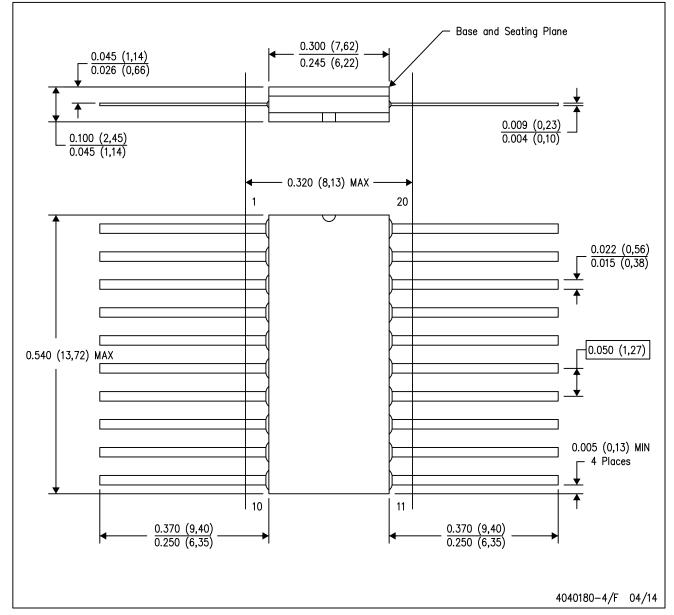

J (R-GDIP-T\*\*) 14 LEADS SHOWN

CERAMIC DUAL IN-LINE PACKAGE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. This package is hermetically sealed with a ceramic lid using glass frit.

- D. Index point is provided on cap for terminal identification only on press ceramic glass frit seal only.

- E. Falls within MIL STD 1835 GDIP1-T14, GDIP1-T16, GDIP1-T18 and GDIP1-T20.

W (R-GDFP-F20)

CERAMIC DUAL FLATPACK

- NOTES: A. All linear dimensions are in inches (millimeters).

- This drawing is subject to change without notice. В.

- C. This package can be hermetically sealed with a ceramic lid using glass frit.

D. Index point is provided on cap for terminal identification only.

E. Falls within Mil-Std 1835 GDFP2-F20

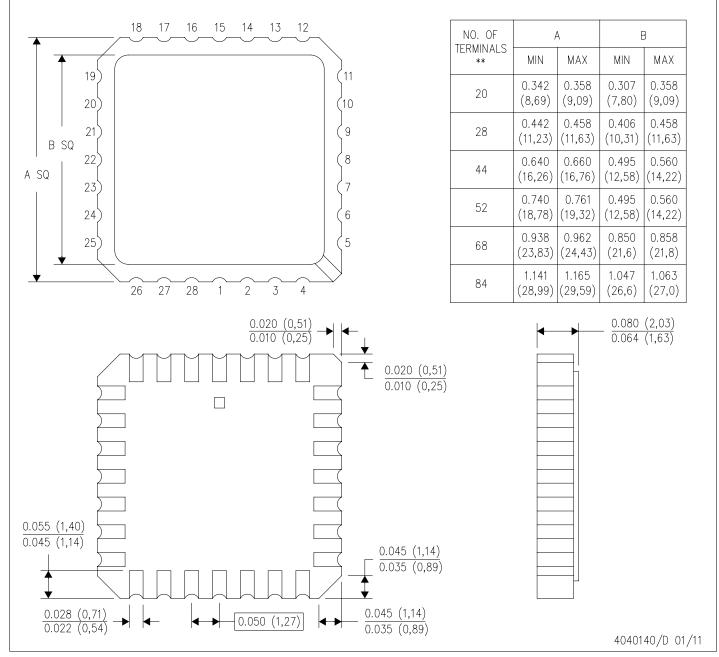

LEADLESS CERAMIC CHIP CARRIER

FK (S-CQCC-N\*\*) 28 TERMINAL SHOWN

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

- C. This package can be hermetically sealed with a metal lid.

- D. Falls within JEDEC MS-004

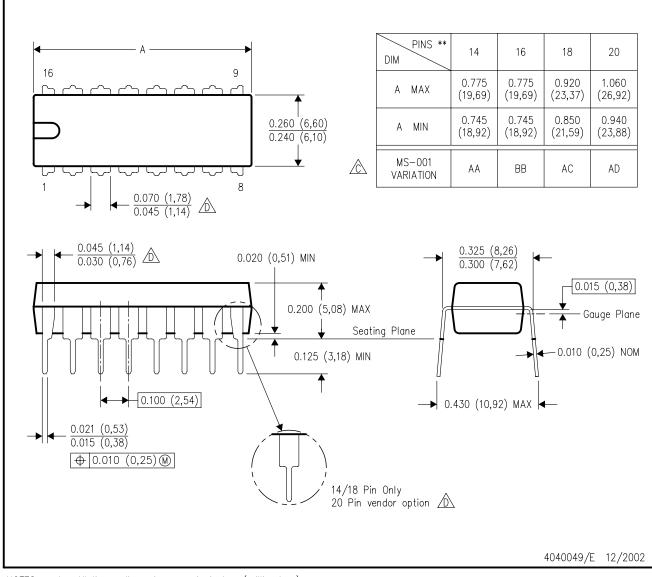

# N (R-PDIP-T\*\*)

PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- $\triangle$  The 20 pin end lead shoulder width is a vendor option, either half or full width.

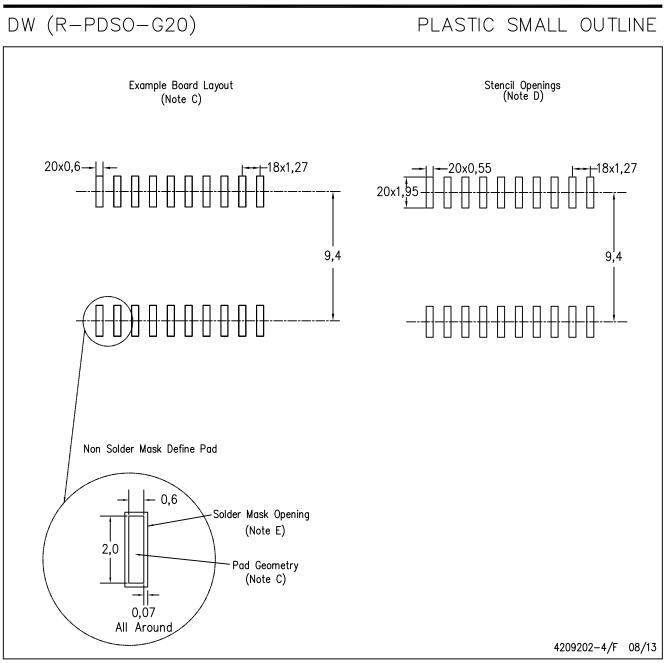

DW (R-PDSO-G20)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters). Dimensioning and tolerancing per ASME Y14.5M-1994.

B. This drawing is subject to change without notice.

C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

D. Falls within JEDEC MS-013 variation AC.

# LAND PATTERN DATA

NOTES:

A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Refer to IPC7351 for alternate board design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

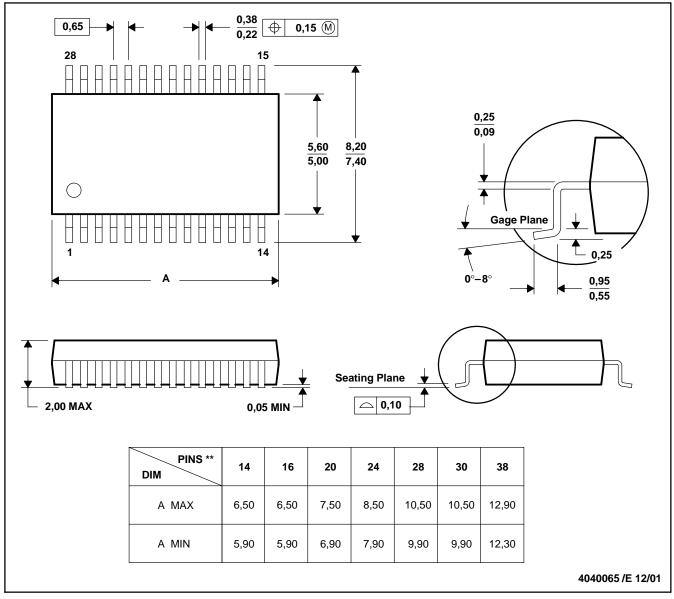

# **MECHANICAL DATA**

MSSO002E - JANUARY 1995 - REVISED DECEMBER 2001

# DB (R-PDSO-G\*\*)

PLASTIC SMALL-OUTLINE

28 PINS SHOWN

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0,15.

- D. Falls within JEDEC MO-150

## MECHANICAL DATA

### PLASTIC SMALL-OUTLINE PACKAGE

#### 0,51 0,35 ⊕0,25⊛ 1,27 8 14 0,15 NOM 5,60 8,20 5,00 7,40 $\bigcirc$ Gage Plane ₽ 0,25 7 1 1,05 0,55 0°-10° Δ 0,15 0,05 Seating Plane — 2,00 MAX 0,10PINS \*\* 14 16 20 24 DIM 10,50 10,50 12,90 15,30 A MAX A MIN 9,90 9,90 12,30 14,70 4040062/C 03/03

NOTES: A. All linear dimensions are in millimeters.

NS (R-PDSO-G\*\*)

**14-PINS SHOWN**

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion, not to exceed 0,15.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated