- 80-ns Instruction Cycle Time

- 544 Words of On-Chip Data RAM

- 4K Words of On-Chip Secure Program EPROM (TMS320E25)

- 4K Words of On-Chip Program ROM (TMS320C25)

- 128K Words of Data/Program Space

- 32-Bit ALU/Accumulator

- 16 × 16-Bit Multiplier With a 32-Bit Product

- Block Moves for Data/Program Management

- Repeat Instructions for Efficient Use of Program Space

- Serial Port for Direct Codec Interface

- Synchronization Input for Synchronous Multiprocessor Configurations

- Wait States for Communication to Slow Off-Chip Memories/Peripherals

- On-Chip Timer for Control Operations

- Single 5-V Supply

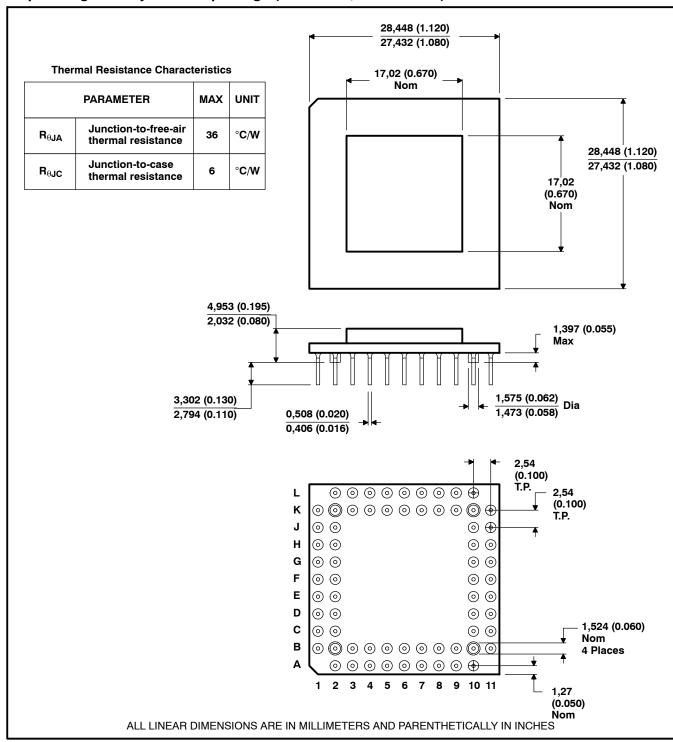

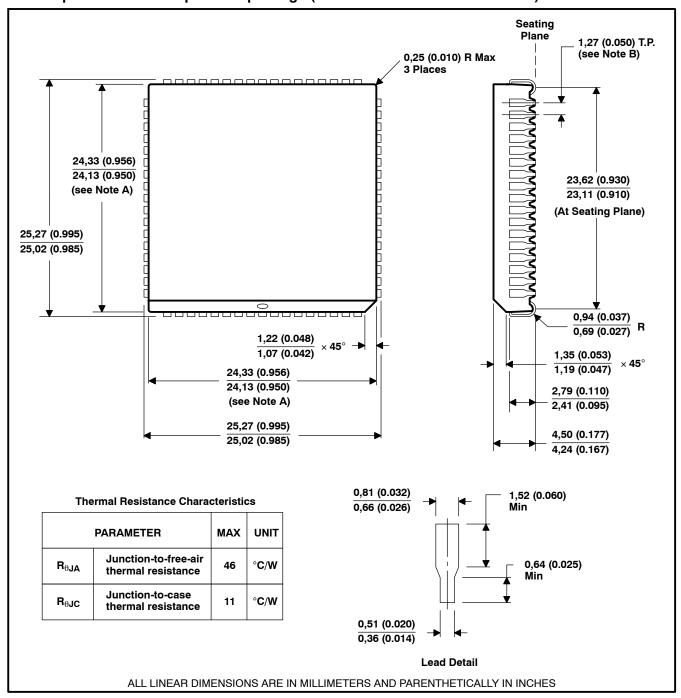

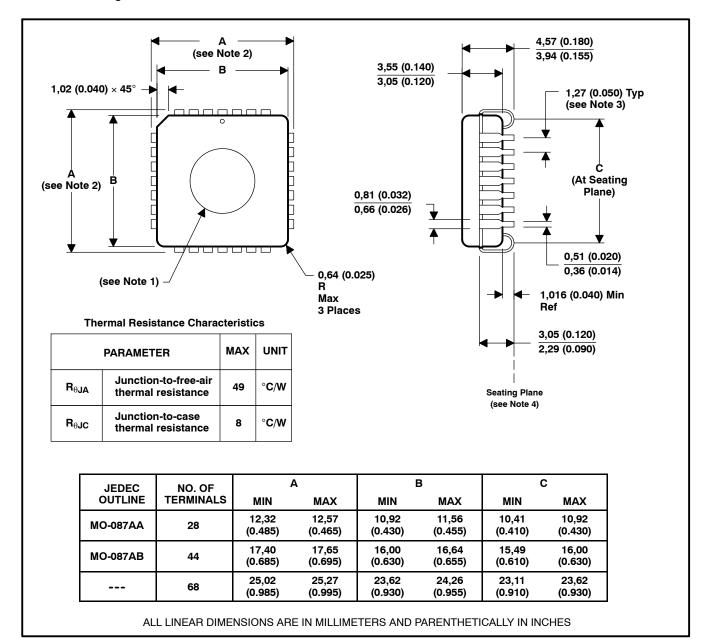

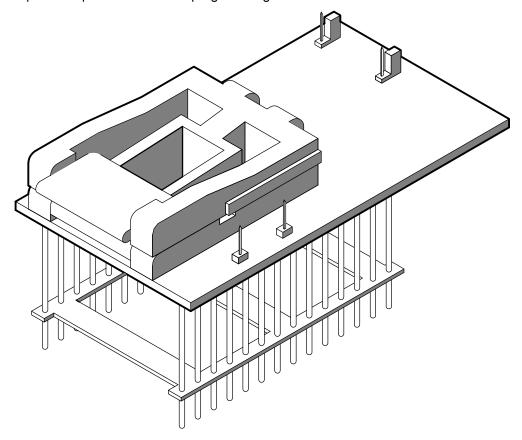

- Packaging: 68-Pin PGA, PLCC, and CER-QUAD

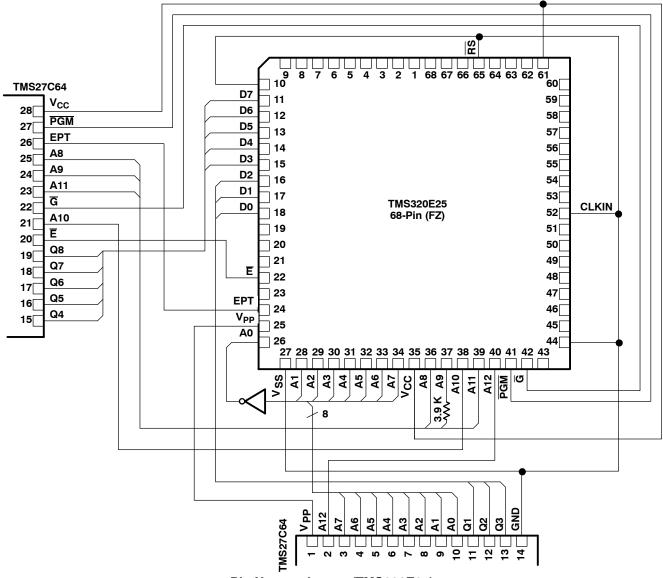

- 68-to-28 Pin Conversion Adapter Socket for EPROM Programming

- Commercial and Military Versions Available

- NMOS Technology:

- TMS32020 ..... 200-ns cycle time

- CMOS Technology:

- TMS320C25 ....... 100-ns cycle time TMS320E25 ...... 100-ns cycle time TMS320C25-50 ..... 80-ns cycle time

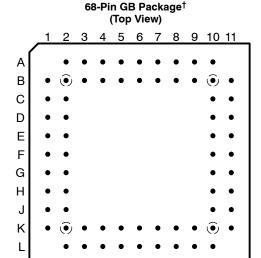

## 68-Pin FN and FZ Packages<sup>†</sup> (Top View)

### description

This data sheet provides complete design documentation for the second-generation devices of the TMS320 family. This facilitates the selection of the devices best suited for user applications by providing all specifications and special features for each TMS320 member. This data sheet is divided into four major sections: architecture, electrical specifications (NMOS and CMOS), timing diagrams, and mechanical data. In each of these sections, generic information is presented first, followed by specific device information. An index is provided for quick reference to specific information about a device.

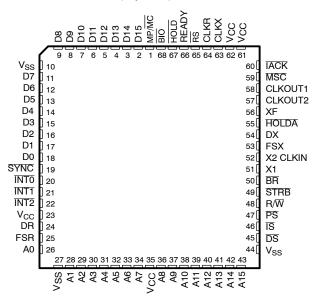

### PGA AND PLCC/CER-QUAD PIN ASSIGNMENTS

| FUNCTION | PIN   | FUNCTION | PIN    | FUNCTION | PIN   | FUNCTION | PIN    | FUNCTION        | PIN    | FUNCTION        | PIN    |

|----------|-------|----------|--------|----------|-------|----------|--------|-----------------|--------|-----------------|--------|

| A0       | K1/26 | A12      | K8/40  | D2       | E1/16 | D14      | A5/3   | ĪNT2            | H1/22  | $V_{CC}$        | H2/23  |

| A1       | K2/28 | A13      | L9/41  | D3       | D2/15 | D15      | B6/2   | ĪS              | J11/46 | V <sub>CC</sub> | L6/35  |

| A2       | L3/29 | A14      | K9/42  | D4       | D1/14 | DR       | J1/24  | MP/MC†          | A6/1   | $V_{SS}$        | B1/10  |

| A3       | K3/30 | A15      | L10/43 | D5       | C2/13 | DS       | K10/45 | MSC             | C10/59 | V <sub>SS</sub> | K11/44 |

| A4       | L4/31 | BIO      | B7/68  | D6       | C1/12 | DX       | E11/54 | PS              | J10/47 | V <sub>SS</sub> | L2/27  |

| A5       | K4/32 | BR       | G11/50 | D7       | B2/11 | FSR      | J2/25  | READY           | B8/66  | XF              | D11/56 |

| A6       | L5/33 | CLKOUT1  | C11/58 | D8       | A2/9  | FSX      | F10/53 | RS              | A8/65  | X1              | G10/51 |

| A7       | K5/34 | CLKOUT2  | D10/57 | D9       | B3/8  | HOLD     | A7/67  | R/W             | H11/48 | X2/CLKIN        | F11/52 |

| A8       | K6/36 | CLKR     | B9/64  | D10      | A3/7  | HOLDA    | E10/55 | STRB            | H10/49 |                 |        |

| A9       | L7/37 | CLKX     | A9/63  | D11      | B4/6  | IACK     | B11/60 | SYNC            | F2/19  |                 |        |

| A10      | K7/38 | D0       | F1/18  | D12      | A4/5  | ĪNT0     | G1/20  | V <sub>CC</sub> | A10/61 |                 |        |

| A11      | L8/39 | D1       | E2/17  | D13      | B5/4  | INT1     | G2/21  | V <sub>CC</sub> | B10/62 |                 | _      |

$<sup>^{\</sup>dagger}$  On the TMS32020, MP/ $\!\overline{\!MC}$  must be connected to  $V_{CC}.$

| SIGNALS         | I/O/Z‡ | DEFINITION                                                                                                          |

|-----------------|--------|---------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub> | I      | 5-V supply pins                                                                                                     |

| $V_{SS}$        | l I    | Ground pins                                                                                                         |

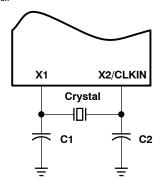

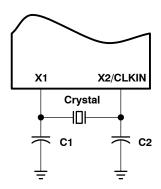

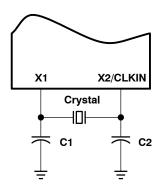

| X1              | 0      | Output from internal oscillator for crystal                                                                         |

| X2/CLKIN        | l I    | Input to internal oscillator from crystal or external clock                                                         |

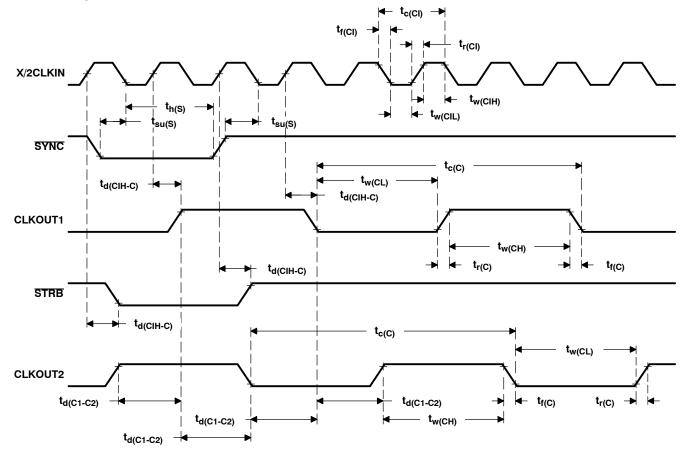

| CLKOUT1         | 0      | Master clock output (crystal or CLKIN frequency/4)                                                                  |

| CLKOUT2         | 0      | A second clock output signal                                                                                        |

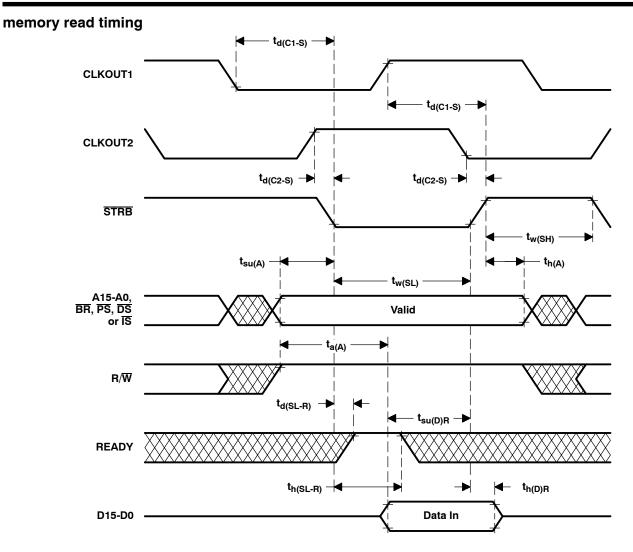

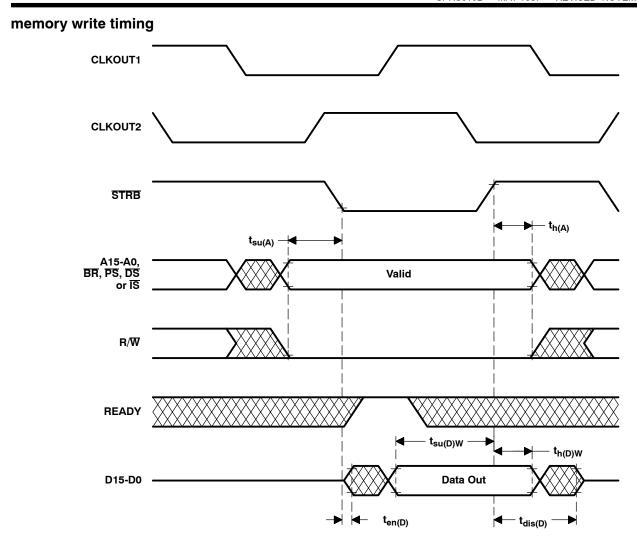

| D15-D0          | I/O/Z  | 16-bit data bus D15 (MSB) through D0 (LSB). Multiplexed between program, data, and I/O spaces.                      |

| A15-A0          | O/Z    | 16-bit address bus A15 (MSB) through A0 (LSB)                                                                       |

| PS, DS, IS      | O/Z    | Program, data, and I/O space select signals                                                                         |

| R/W             | O/Z    | Read/write signal                                                                                                   |

| STRB            | O/Z    | Strobe signal                                                                                                       |

| RS              | - 1    | Reset input                                                                                                         |

| INT2-INT0       | l I    | External user interrupt inputs                                                                                      |

| MP/MC           | l I    | Microprocessor/microcomputer mode select pin                                                                        |

| MSC             | 0      | Microstate complete signal                                                                                          |

| <b>IACK</b>     | 0      | Interrupt acknowledge signal                                                                                        |

| READY           | - 1    | Data ready input. Asserted by external logic when using slower devices to indicate that the current bus transaction |

|                 |        | is complete.                                                                                                        |

| BR              | 0      | Bus request signal. Asserted when the TMS320C2x requires access to an external global data memory space.            |

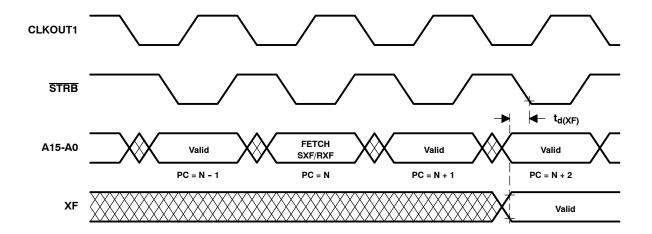

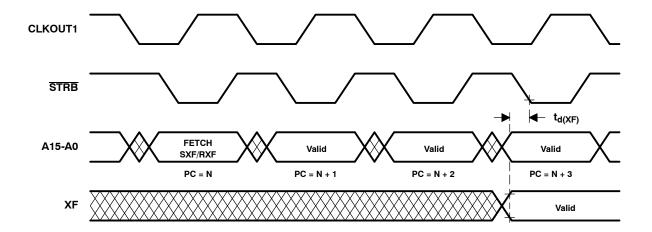

| XF              | 0      | External flag output (latched software-programmable signal)                                                         |

| HOLD            | l I    | Hold input. When asserted, TMS320C2x goes into an idle mode and places the data, address, and control lines in      |

|                 |        | the high impedance state.                                                                                           |

| HOLDA           | 0      | Hold acknowledge signal                                                                                             |

| SYNC            | - 1    | Synchronization input                                                                                               |

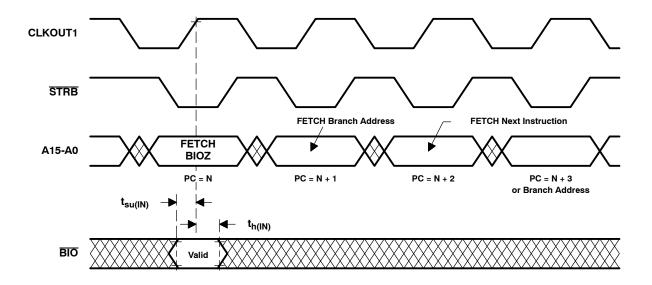

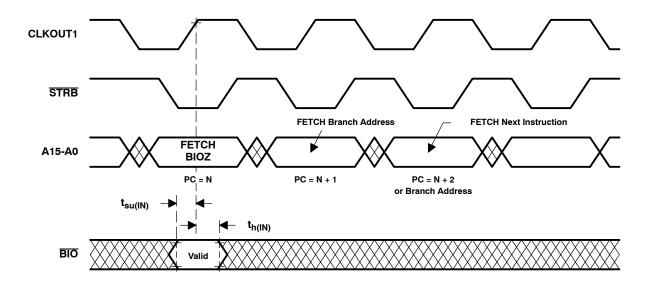

| BIO             | - 1    | Branch control input. Polled by BIOZ instruction.                                                                   |

| DR              | l I    | Serial data receive input                                                                                           |

| CLKR            | - 1    | Clock for receive input for serial port                                                                             |

| FSR             | I      | Frame synchronization pulse for receive input                                                                       |

| DX              | O/Z    | Serial data transmit output                                                                                         |

| CLKX            | I      | Clock for transmit output for serial port                                                                           |

| FSX             | I/O/Z  | Frame synchronization pulse for transmit. Configuration as either an input or an output.                            |

<sup>&</sup>lt;sup>‡</sup> I/O/Z denotes input/output/high-impedance state.

### description

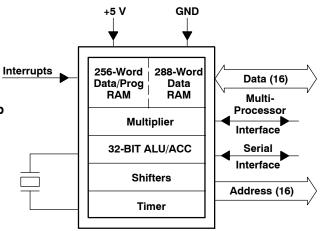

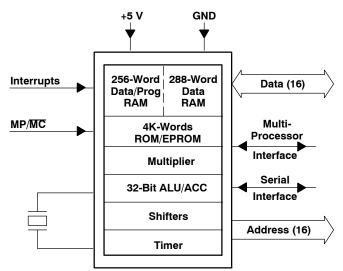

The TMS320 family of 16/32-bit single-chip digital signal processors combines the flexibility of a high-speed controller with the numerical capability of an array processor, thereby offering an inexpensive alternative to multichip bit-slice processors. The highly paralleled architecture and efficient instruction set provide speed and flexibility to produce a MOS microprocessor family that is capable of executing more than 12.5 MIPS (million instructions per section). The TMS320 family optimizes speed by implementing functions in hardware that other processors implement through microcode or software. This hardware-intensive approach provides the design engineer with processing power previously unavailable on a single chip.

The TMS320 family consists of three generations of digital signal processors. The first generation contains the TMS32010 and its spinoffs. The second generation includes the TMS32020, TMS320C25, and TMS320E25, which are described in this data sheet. The TMS320C30 is a floating-point DSP device designed for even higher performance. Many features are common among the TMS320 processors. Specific features are added in each processor to provide different cost/performance tradeoffs. Software compatibility is maintained throughout the family to protect the user's investment in architecture. Each processor has software and hardware tools to facilitate rapid design.

### introduction

The TMS32010, the first NMOS digital signal processor in the TMS320 family, was introduced in 1983. Its powerful instruction set, inherent flexibility, high-speed number-crunching capabilities, and innovative architecture have made this high-performance, cost-effective processor the ideal solution to many telecommunications, computer, commercial, industrial, and military applications. Since that time, the TMS320C10, a low-power CMOS version of the industry-standard TMS32010, and other spinoff devices have been added to the first generation of the TMS320 family.

The second generation of the TMS320 family (referred to as TMS320C2x) includes four members, the TMS32020, TMS320C25, TMS320C25-50, and TMS320E25. The architecture of these devices is based upon that of the TMS32010.

The **TMS32020**, processed in NMOS technology, is source-code compatible with he TMS32010 and in many applications is capable of two times the throughput of the first-generation devices. Its enhanced instruction set (109 instructions), large on-chip data memory (544 words), large memory spaces, on-chip serial port, and hardware timer make the TMS32020 a powerful addition to the TMS320 family.

The **TMS320C25** is the second member of the TMS320 second generation. It is processed in CMOS technology, is capable of an instruction cycle time of 100 ns, and is pin-for-pin and object-code compatible with the TMS32020. The TMS320C25's enhanced feature set greatly increases the functionality of the device over the TMS32020. Enhancements included 24 additional instructions (133 total), eight auxiliary registers, an eight-level hardware stack, 4K words of on-chip program ROM, a bit-reversed indexed-addressing mode, and the low-power dissipation inherent to the CMOS process. An extended-temperature range version (TMS320C25GBA) is also available.

The **TMS320C25-50** is a high-speed version of the TMS320C25. It is capable of an instruction cycle time of less than 80 ns. It is architecturally identical to the original 40-MHz version of the TMS320C25 and, thus, is pin-for-pin and object-code compatible with the TMS320C25.

The **TMS320E25** is identical to the TMS320C25, with the exception that the on-chip 4K-word program ROM is replaced with a 4K-word on-chip program EPROM. On-chip EPROM allows realtime code development and modification for immediate evaluation of system performance.

### **Key Features: TMS32020**

- 200-ns Instruction Cycle Time

- 544 Words of On-Chip Data RAM

- 128K Words of Total Data/Program Memory Space

- Wait States for Communication to Slower Off-Chip Memories

- Source Code Compatible With the TMS320C1x

- Single-Cycle Multiply/Accumulate Instructions

- Repeat Instructions

- Global Data Memory Interface

- Block Moves for Data/Program Management

- Five Auxiliary Registers With Dedicated Arithmetic Unit

- Serial Port for Multiprocessing or Interfacing to Codecs, Serial Analog-to-Digital Converters, etc.

### Key Features: TMS320C25, TMS320C25-50, TMS320E25

- 80-ns Instruction Cycle Time (TMS320C25-50)

- 100-ns Instruction Cycle Time (TMS320C25)

- 4K Words of On-Chip Secure Program EPROM (TMS320E25)

- 4K Words of On-Chip Program ROM (TMS320C25)

- 544 Words of On-Chip RAM

- 128K Words of Total Program/Data Memory Space

- Wait States for Communications to Slower Off-Chip Memories

- Object-Code Compatible With the TMS32020

- Source-Code Compatible With TMS320C1x

- 24 Additional Instructions to Support Adaptive Filtering, FFTs, and Extended-Precision Arithmetic

- Block Moves for Data/Program Management

- Single-Cycle Multiply/Accumulate Instructions

- Eight Auxiliary Registers With Dedicated Arithmetic Unit

- Bit-Reversed Indexed-Addressing Mode for Radix-2 FFTS

- Double-Buffered Serial Port

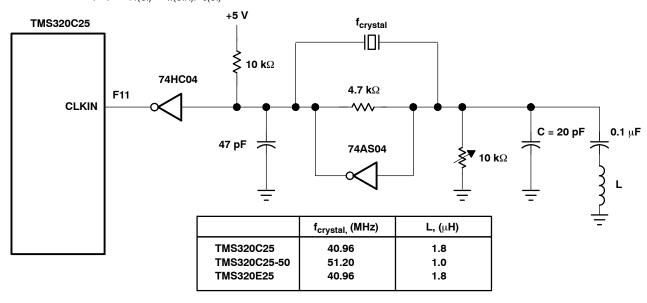

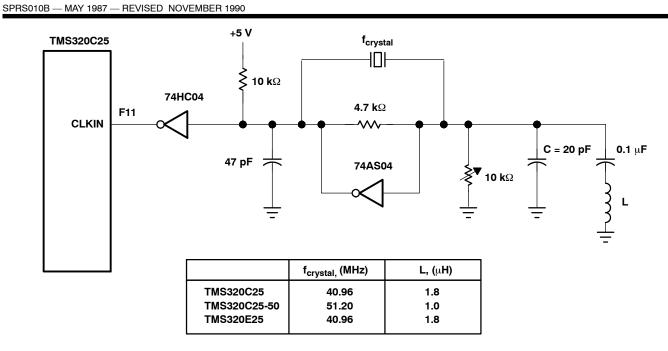

- On-Chip Clock Generator

- Single 5-V Supply

- NMOS Technology

- 68-Pin Grid Array (PGA) Package

- On-Chip Clock Generator

- Single 5-V Supply

- Internal Security Mechanism (TMS320E25)

- 68-to-28 Pin Conversion Adapter Socket

- CMOS Technology

- 68-Pin Grid Array (PGA) Package (TMS320C25)

- 68-Lead Plastic Leaded Chip Carrier (PLCC)

Package (TMS320C25, TMS320C25-50)

- 68-Lead CER-QUAD Package (TMS320E25)

Table 1 provides an overview of the second-generation TMS320 processors with comparisons of memory, I/O, cycle timing, power, package type, technology, and military support. For specific availability, contact the nearest TI Field Sales Office.

Table 1. TMS320 Second-Generation Device Overview

|                        |        |     | MEMORY    | ,     |      |     | L/O†    |     |       | CYCLE | TYP   |     | PACK | AGE      |

|------------------------|--------|-----|-----------|-------|------|-----|---------|-----|-------|-------|-------|-----|------|----------|

| DEVICE                 |        | (   | ON-CHIP   | OFF-0 | CHIP |     | I/O†    |     | TIMER | TIME  | POWER |     | TYI  | PE       |

|                        |        | RAM | ROM/EPROM | PROG  | DATA | SER | PAR     | DMA |       | (ns)  | (mW)  | PGA | PLCC | CER-QUAD |

| TMS32020 <sup>‡</sup>  | (NMOS) | 544 | -         | 64K   | 64K  | YES | 16 × 16 | YES | YES   | 200   | 1250  | 68  | _    | _        |

| TMS320C25 <sup>‡</sup> | (CMOS) | 544 | 4K        | 64K   | 64K  | YES | 16 × 16 | CON | YES   | 100   | 500   | 68  | 68   | 1        |

| TMS320C25-50§          | (CMOS) | 544 | 4K        | 64K   | 64K  | YES | 16 × 16 | CON | YES   | 80    | 500   | _   | 68   | _        |

| TMS320E25§             | (CMOS) | 544 | 4K        | 64K   | 64K  | YES | 16 × 16 | CON | YES   | 100   | 500   | _   | _    | 68       |

<sup>&</sup>lt;sup>†</sup> SER = serial; PAR = parallel; DMA = direct memory access; CON = concurrent DMA.

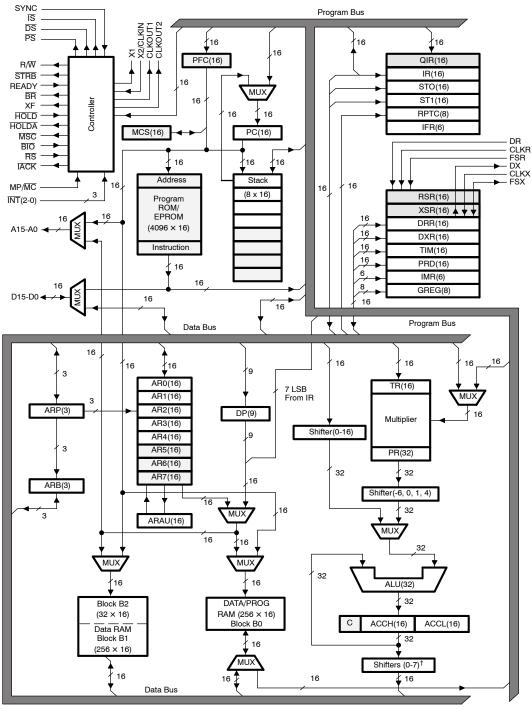

### architecture

The TMS320 family utilizes a modified Harvard architecture for speed and flexibility. In a strict Harvard architecture, program and data memory lie in two separate spaces, permitting a full overlap of instruction fetch and execution. The TMS320 family's modification of the Harvard architecture allows transfers between program and data spaces, thereby increasing the flexibility of the device. This modification permits coefficients stored in program memory to be read into the RAM, eliminating the need for a separate coefficient ROM. It also makes available immediate instructions and subroutines based on computed values.

Increased throughput on the TMS320C2x devices for many DSP applications is accomplished by means of single-cycle multiply/accumulate instructions with a data move option, up to eight auxiliary registers with a dedicated arithmetic unit, and faster I/O necessary for data-intensive signal processing.

The architectural design of the TMS320C2x emphasizes overall speed, communication, and flexibility in processor configuration. Control signals and instructions provide floating-point support, block-memory transfers, communication to slower off-chip devices, and multiprocessing implementations.

### 32-bit ALU/accumulator

The 32-bit Arithmetic Logic Unit (ALU) and accumulator perform a wide range of arithmetic and logical instructions, the majority of which execute in a single clock cycle. The ALU executes a variety of branch instructions dependent on the status of the ALU or a single bit in a word. These instructions provide the following capabilities:

- Branch to an address specified by the accumulator

- Normalize fixed-point numbers contained in the accumulator

- Test a specified bit of a word in data memory

One input to the ALU is always provided from the accumulator, and the other input may be provided from the Product Register (PR) of the multiplier or the input scaling shifter which has fetched data from the RAM on the data bus. After the ALU has performed the arithmetic or logical operations, the result is stored in the accumulator.

The 32-bit accumulator is split into two 16-bit segments for storage in data memory. Additional shifters at the output of the accumulator perform shifts while the data is being transferred to the data bus for storage. The contents of the accumulator remain unchanged.

<sup>&</sup>lt;sup>‡</sup> Military version available; contact nearest TI Field Sales Office for availability.

<sup>§</sup> Military version planned; contact nearest TI Field Sales Office for details.

### functional block diagram (TMS320C2x)

| L | EG | ìΕ | NE | ): |

|---|----|----|----|----|

Interrupt flag registerInterrupt mask register ACCH Accumulator high IFR ACCL Accumulator low IMR PFC RPTC ALU Arithmetic logic unit IR Instruction register Auxiliary register arithmetic unitMCS Auxiliary register pointer buffer GREG ARAU Microcall stack Queue instruction register ARB QIR RSR Auxiliary register pointer Product register DP Data memory page pointer PRD Period register for timer DRR Serial port data receive registerTIM

TR

Serial port data transmit register

XSR = Serial port transmit shift register

ner AR0-AR7 = Auxiliary registers

ST0, ST1 = Status registers

C = Carry bit

Program counter

Prefetch counter

Repeat instruction counter

Global memory allocation register

= Serial port receive shift register

Temporary register

### scaling shifter

The TMS320C2x scaling shifter has 16-bit input connected to the data bus and a 32-bit output connected to the ALU. The scaling shifter produces a left shift of 0 to 16 bits on the input data, as programmed in the instruction. The LSBs of the output are filled with zeroes, and the MSBs may be either filled with zeroes or sign-extended, depending upon the status programmed into the SXM (sign-extension mode) bit of status register ST1.

### 16 × 16-bit parallel multiplier

The 16  $\times$  16-bit hardware multiplier is capable of computing a signed or unsigned 32-bit product in a single machine cycle. The multiplier has the following two associated registers.

- A 16-bit Temporary Register (TR) that holds one of the operands for the multiplier, and

- A 32-bit Product Register (PR) that holds the product.

Incorporated into the instruction set are single-cycle multiply/accumulate instructions that allow both operands to be processed simultaneously. The data for these operations may reside anywhere in internal or external memory, and can be transferred to the multiplier each cycle via the program and data buses.

Four product shift modes are available at the Product Register (PR) output that are useful when performing multiply/accumulate operations, fractional arithmetic, or justifying fractional products.

### timer

The TMS320C2x provides a memory-mapped 16-bit timer for control operations. The on-chip timer (TIM) register is a down counter that is continuously clocked by CLKOUT1 on the TMS320C25. The timer is clocked by CLKOUT1/4 on the TMS32020. A timer interrupt (TINT) is generated every time the timer decrements to zero. The timer is reloaded with the value contained in the period (PRD) register within the next cycle after it reaches zero so that interrupts may be programmed to occur at regular intervals of PRD + 1 cycles of CLKOUT 1 on the TMS320C25 or  $4 \times PRD \times CLKOUT$  1 cycles on the TMS32020.

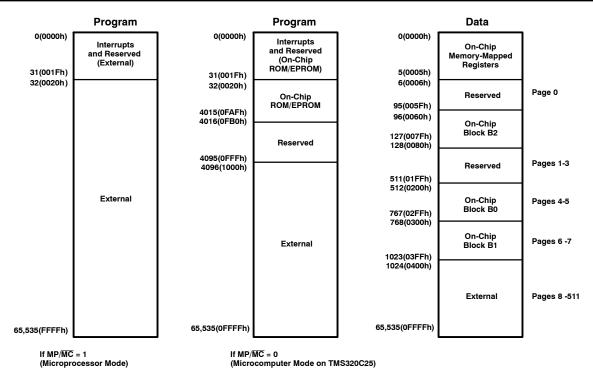

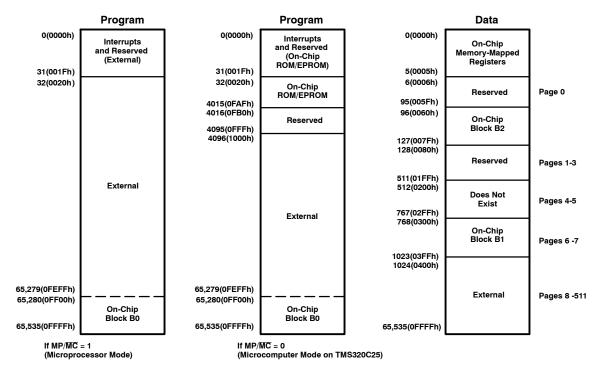

### memory control

The TMS320C2x provides a total of 544 16-bit words of on-chip data RAM, divided into three separate blocks (B0, B1, and B2). Of the 544 words, 288 words (blocks B1 and B2) are always data memory, and 256 words (block B0) are programmable as either data or program memory. A data memory size of 544 words allows the TMS320C2x to handle a data array of 512 words (256 words if on-chip RAM is used for program memory), while still leaving 32 locations for intermediate storage. When using block B0 as program memory, instructions can be downloaded from external program memory into on-chip RAM and then executed.

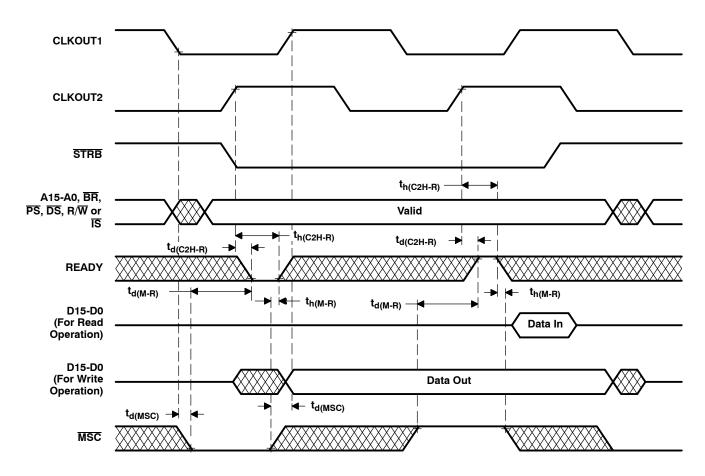

When using on-chip program RAM, ROM, EPROM, or high-speed external program memory, the TMS320C2x runs at full speed without wait states. However, the READY line can be used to interface the TMS320C2x to slower, less-expensive external memory. Downloading programs from slow off-chip memory to on-chip program RAM speeds processing while cutting system costs.

The TMS320C2x provides three separate address spaces for program memory, data memory, and I/O. The on-chip memory is mapped into either the 64K-word data memory or program memory space, depending upon the memory configuration (see Figure 1). The CNFD (configure block B0 as data memory) and CNFP (configure block B0 as program memory) instructions allow dynamic configuration of the memory maps through software. Regardless of the configuration, the user may still execute from external program memory.

The TMS320C2x has six registers that are mapped into the data memory space: a serial port data receive register, serial port data transmit register, timer register, period register, interrupt mask register, and global memory allocation register.

### (a) Memory Maps After a CNFD Instruction

(b) Memory Maps After a CNFP Instruction

Figure 1. Memory Maps

### interrupts and subroutines

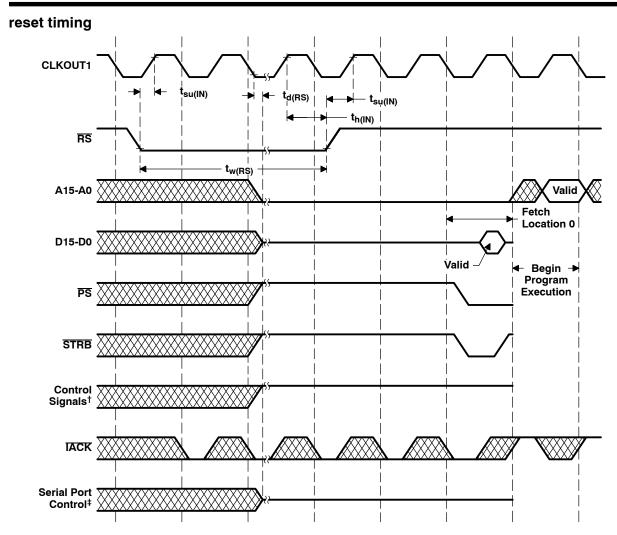

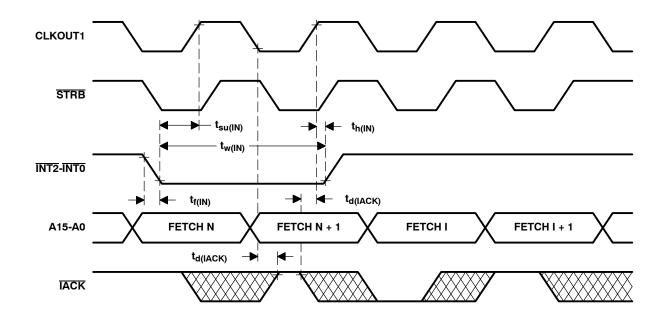

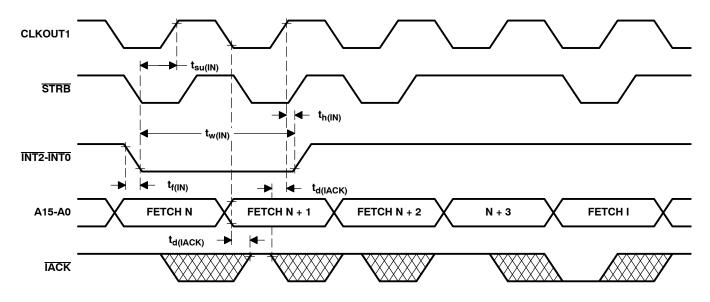

The TMS320C2x has three external maskable user interrupts  $\overline{\text{INT2-INT0}}$ , available for external devices that interrupt the processor. Internal interrupts are generated by the serial port (RINT and XINT), by the timer (TINT), and by the software interrupt (TRAP) instruction. Interrupts are prioritized with reset (RS) having the highest priority and the serial port transmit interrupt (XINT) having the lowest priority. All interrupt locations are on two-word boundaries so that branch instructions can be accommodated in those locations if desired.

A built-in mechanism protects multicycle instructions from interrupts. If an interrupt occurs during a multicycle instruction, the interrupt is not processed until the instruction is completed. This mechanism applies to instructions that are repeated and to instructions that become multicycle due to the READY signal.

### external interface

The TMS320C2x supports a wide range of system interfacing requirements. Program, data, and I/O address spaces provide interface to memory and I/O, thus maximizing system throughput. I/O design is simplified by having I/O treated the same way as memory. I/O devices are mapped into the I/O address space using the processor's external address and data buses in the same manner as memory-mapped devices. Interface to memory and I/O devices of varying speeds is accomplished by using the READY line. When transactions are made with slower devices, the TMS320C2x processor waits until the other device completes its function and signals the processor via the READY line. Then, the TMS320C2x continues execution.

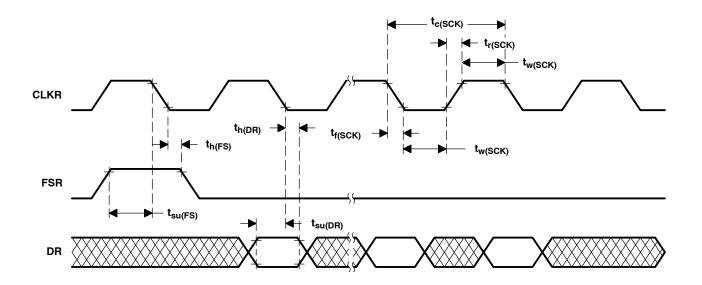

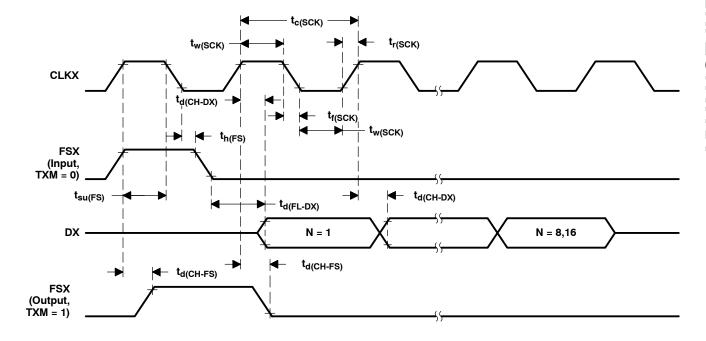

A full-duplex serial port provides communication with serial devices, such as codecs, serial A/D converters, and other serial systems. The interface signals are compatible with codecs and many other serial devices with a minimum of external hardware. The serial port may also be used for intercommunication between processors in multiprocessing applications.

The serial port has two memory-mapped registers: the data transmit register (DXR) and the data receive register (DRR). Both registers operate in either the byte mode or 16-bit word mode, and may be accessed in the same manner as any other data memory location. Each register has an external clock, a framing synchronization pulse, and associated shift registers. One method of multiprocessing may be implemented by programming one device to transmit while the others are in the receive mode. The serial port on the TMS320C25 is double-buffered and fully static.

### multiprocessing

The flexibility of the TMS320C2x allows configurations to satisfy a wide range of system requirements and can be used as follows:

- A standalone processor

- A multiprocessor with devices in parallel

- A slave/host multiprocessor with global memory space

- A peripheral processor interfaced via processor-controlled signals to another device.

For multiprocessing applications, the TMS320C2x has the capability of allocating global data memory space and communicating with that space via the  $\overline{BR}$  (bus request) and READY control signals. Global memory is data memory shared by more than one processor. Global data memory access must be arbitrated. The 8-bit memory-mapped GREG (global memory allocation register) specifies part of the TMS320C2x's data memory as global external memory. The contents of the register determine the size of the global memory space. If the current instruction addresses an operand within that space,  $\overline{BR}$  is asserted to request control of the bus. The length of the memory cycle is controlled by the READY line.

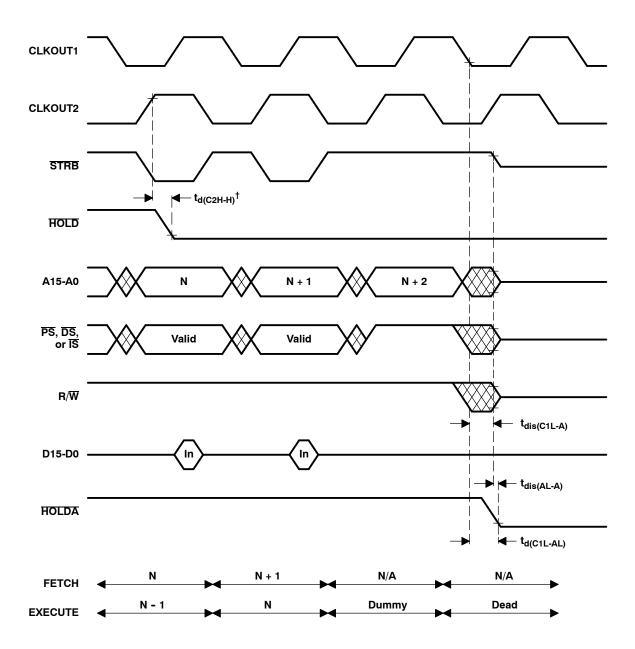

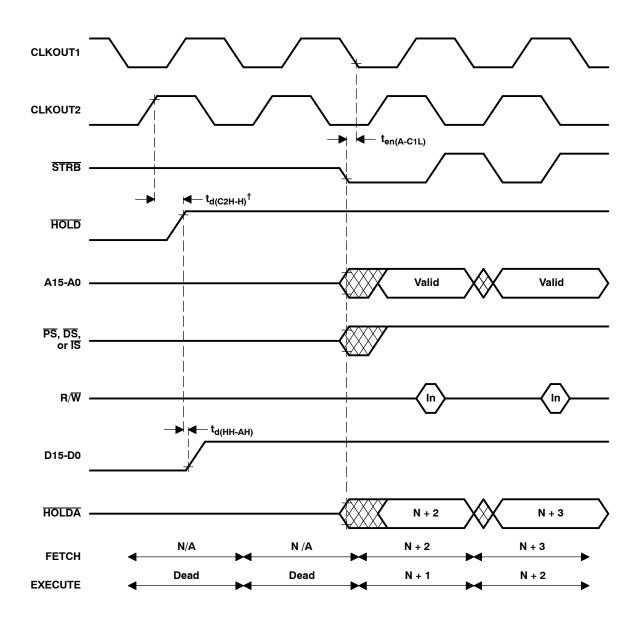

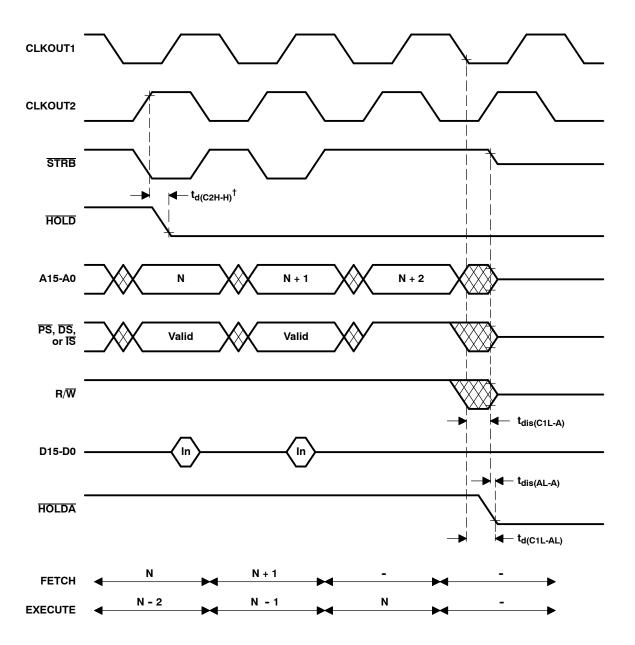

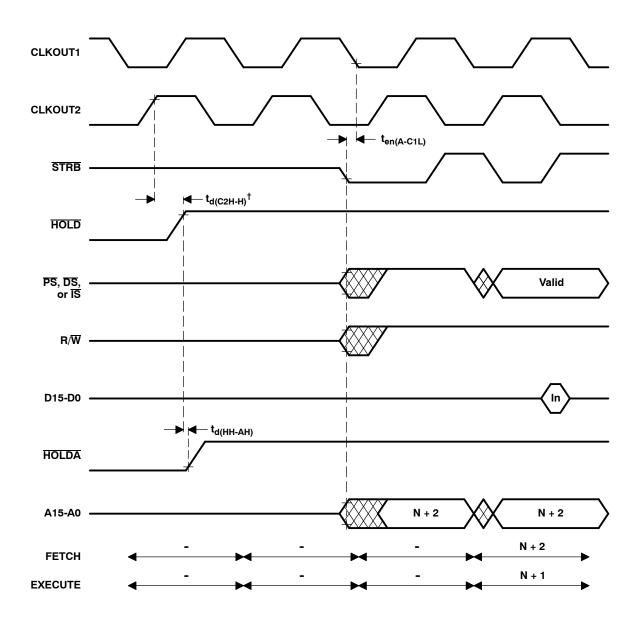

The TMS320C2x supports DMA (direct memory access) to its external program/data memory using the HOLD and HOLDA signals. Another processor can take complete control of the TMS320C2x's external memory by asserting HOLD low. This causes the TMS320C2x to place its address data and control lines in a high-impedance state, and assert HOLDA. On the TMS320C2x, program execution from on-chip ROM may proceed concurrently when the device is in the hold mode.

## TMS320 SECOND GENERATION DIGITAL SIGNAL PROCESSORS

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

### instruction set

The TMS320C2x microprocessor implements a comprehensive instruction set that supports both numeric-intensive signal processing operations as well as general-purpose applications, such as multiprocessing and high-speed control. The TMS320C20 source code is upward-compatible with TMS320C25 source code. TMS320C20 object code runs directly on the TMS320C25.

For maximum throughput, the next instruction is prefetched while the current one is being executed. Since the same data lines are used to communicate to external data/program or I/O space, the number of cycles may vary depending upon whether the next data operand fetch is from internal or external memory. Highest throughput is achieved by maintaining data memory on-chip and using either internal or fast external program memory.

### addressing modes

The TMS320C2x instruction set provides three memory addressing modes: direct, indirect, and immediate addressing.

Both direct and indirect addressing can be used to access data memory. In direct addressing, seven bits of the instruction word are concatenated with the nine bits of the data memory page pointer to form the 16-bit data memory address. Indirect addressing accesses data memory through the auxiliary registers. In immediate addressing, the data is based on a portion of the instruction word(s).

In direct memory addressing, the instruction word contains the lower seven bits of the data memory address. This field is concatenated with the nine bits of the data memory page pointer to form the full 16-bit address. Thus, memory is paged in the direct addressing mode with a total of 512 pages, each page containing 128 words.

Up to eight auxiliary registers (AR0-AR7) provide flexible and powerful indirect addressing (five on the TMS320C25). To select a specific auxiliary register, the Auxiliary Register Pointer (ARP) is loaded with a value from 0 to 7 for AR0 through AR7, respectively.

There are seven types of indirect addressing: auto-increment or auto-decrement, post-indexing by either adding or subtracting the contents of AR0, single indirect addressing with no increment or decrement, and bit-reversal addressing (used in FFTs on the TMS320C25 only) with increment or decrement. All operations are performed on the current auxiliary register in the same cycle as the original instruction, following which the current auxiliary register and ARP may be modified.

### repeat feature

A repeat feature, used with instructions such as multiply/accumulates, block moves, I/O transfers, and table read/writes, allows a single instruction to be performed up to 256 times. The repeat counter (RPTC) is loaded with either a data memory value (RPT instruction) or an immediate value (RPTK instruction). The value of this operand is one less than the number of times that the next instruction is executed. Those instructions that are normally multicycle are pipelined when using the repeat feature, and effectively become single-cycle instructions.

SPRS010B — MAY 1987 — REVISED NOVEMBER 1990

### instruction set summary

Table 2 lists the symbols and abbreviations used in Table 3, the TMS320C25 instruction set summary. Table 3 consists primarily of single-cycle, single-word instructions. Infrequently used branch, I/O, and CALL instructions are multicycle. The instruction set summary is arranged according to function and alphabetized within each functional grouping. The symbol (†) indicates those instructions that are not included in the TMS320C1x instruction set. The symbol (‡) indicates instructions that are not included in the TMS32020 instruction set.

**Table 2. Instruction Symbols**

| SYMBOL | DEFINITION                                                      |

|--------|-----------------------------------------------------------------|

| В      | 4-bit field specifying a bit code                               |

| CM     | 2-bit field specifying compare mode                             |

| D      | Data memory address field                                       |

| FO     | Format status bit                                               |

| 1      | Addressing mode bit                                             |

| K      | Immediate operand field                                         |

| PA     | Port address (PA0 through PA15 are predefined assembler symbols |

|        | equal to 0 through 15, respectively.)                           |

| PM     | 2-bit field specifying P register output shift code             |

| AR     | 3-bit operand field specifying auxiliary register               |

| S      | 4-bit left-shift code                                           |

| X      | 3-bit accumulator left-shift field                              |

### Table 3. TMS320C25 Instruction Set Summary

|                   | ACCUMULATOR ME                                               | MORY RE | FER | ENC | E IN | STRU | JCTI | ONS | ,    |            |     |     |    |     |       |   |   |          |

|-------------------|--------------------------------------------------------------|---------|-----|-----|------|------|------|-----|------|------------|-----|-----|----|-----|-------|---|---|----------|

| MNEMONIC          | DESCRIPTION                                                  | NO.     |     |     |      |      | INS  | TRU | JCTI | ON I       | ВІТ | COI | DΕ |     |       |   |   |          |

|                   |                                                              | WORDS   | 15  | 14  | 13   | 12   | 11   | 10  | 9    | 8          | 7   | 6   | 5  | 4   | 3     | 2 | 1 | 0        |

| ABS               | Absolute value of accumulator                                | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 0  | 1   | 1     | 0 | 1 | 1        |

| ADD               | Add to accumulator with shift                                | 1       | 0   | 0   | 0    | 0    | •    |     | s—   | <b></b> ▶  | 1   | •   |    |     | - D - |   |   | <b>→</b> |

| ADDC‡             | Add to accumulator with carry                                | 1       | 0   | 1   | 0    | 0    | 0    | 0   | 1    | 1          | 1   | 4   |    |     | - D-  |   |   | →        |

| ADDH              | Add to high accumulator                                      | 1       | 0   | 1   | 0    | 0    | 1    | 0   | 0    | 0          | 1   | •   |    |     | - D - |   | — | <b>→</b> |

| ADDK‡             | Add to accumulator short immediate                           | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 0    | 0          | •   |     |    | — k | (—    |   | — | <b>→</b> |

| ADDS              | Add to low accumulator with sign extension suppressed        | 1       | 0   | 1   | 0    | 0    | 1    | 0   | 0    | 1          | ı   | •   |    |     | - D-  |   | — | <b>→</b> |

| ADDT              | Add to accumulator with shift specified by T register        | 1       | 0   | 1   | 0    | 0    | 1    | 0   | 1    | 0          | I   | •   |    |     | - D-  |   | — | <b>→</b> |

| ADLK <sup>†</sup> | Add to accumulator long immediate with shift                 | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b> ► | 0   | 0   | 0  | 0   | 0     | 0 | 1 | 0        |

| AND               | AND with accumulator                                         | 1       | 0   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | ı   | 4   |    |     | - D-  |   |   | <b>→</b> |

| ANDK†             | AND immediate with accumulator with shift                    | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b></b> ▶  | 0   | 0   | 0  | 0   | 0     | 1 | 0 | 0        |

| CMPL <sup>†</sup> | Complement accumulator                                       | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 0   | 0     | 1 | 1 | 1        |

| LAC               | Load accumulator with shift                                  | 1       | 0   | 0   | 1    | 0    | •    |     | s—   | <b>-</b> ► | 1   | 4   |    |     | - D - |   |   | <b>→</b> |

| LACK              | Load accumulator immediate short                             | 1       | 1   | 1   | 0    | 0    | 1    | 0   | 1    | 0          | 4   |     |    | — k | (—    |   |   | <b>→</b> |

| LACT <sup>†</sup> | Load accumulator with shift specified by T register          | 1       | 0   | 1   | 0    | 0    | 0    | 0   | 1    | 0          | ı   | 4   |    |     | - D-  |   |   | <b>→</b> |

| LALK <sup>†</sup> | Load accumulator long immediate with shift                   | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b></b> ▶  | 0   | 0   | 0  | 0   | 0     | 0 | 0 | 1        |

| NEG <sup>†</sup>  | Negate accumulator                                           | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 0   | 0     | 0 | 1 | 1        |

| NORM <sup>†</sup> | Normalize contents of accumulator                            | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 1   | Х   | Χ  | Х   | 0     | 0 | 1 | 0        |

| OR                | OR with accumulator                                          | 1       | 0   | 1   | 0    | 0    | 1    | 1   | 0    | 1          | 1   | •   |    |     | - D-  |   |   | <b>→</b> |

| ORK†              | OR immediate with accumulator with shift                     | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b></b> ▶  | 0   | 0   | 0  | 0   | 0     | 1 | 0 | 1        |

| ROL‡              | Rotate accumulator left                                      | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 1   | 0     | 1 | 0 | 0        |

| ROR <sup>‡</sup>  | Rotate accumulator right                                     | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 1  | 1   | 0     | 1 | 0 | 1        |

| SACH              | Store high accumulator with shift                            | 1       | 0   | 1   | 1    | 0    | 1    | •   | - x  | <b></b> ▶  | - 1 | •   |    |     | - D-  |   |   | <b>→</b> |

| SACL              | Store low-order accumulator with shift                       | 1       | 0   | 1   | 1    | 0    | 0    | •   | - x  | <b>-</b> ▶ | - 1 | •   |    |     | - D-  |   |   | <b>→</b> |

| SBLK†             | Subtract from accumulator long immediate with shift          | 2       | 1   | 1   | 0    | 1    | •    |     | s—   | <b>-</b>   | 0   | 0   | 0  | 0   | 0     | 0 | 1 | 1        |

| SFL <sup>†</sup>  | Shift accumulator left                                       | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 0  | 1   | 1     | 0 | 0 | 0        |

| SFR <sup>†</sup>  | Shift accumulator right                                      | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 1    | 0          | 0   | 0   | 0  | 1   | 1     | 0 | 0 | 1        |

| SUB               | Subtract from accumulator with shift                         | 1       | 0   | 0   | 0    | 1    | •    |     | s—   | <b></b> ▶  | - 1 | •   |    |     | - D-  |   |   | <b>→</b> |

| SUBB‡             | Subtract from accumulator with borrow                        | 1       | 0   | 1   | 0    | 0    | 1    | 1   | 1    | 1          | ı   | 4   |    |     | - D-  |   |   | <b>→</b> |

| SUBC              | Conditional subtract                                         | 1       | 0   | 1   | 0    | 0    | 0    | 1   | 1    | 1          | ı   | 4   |    |     | - D-  |   |   | <b>→</b> |

| SUBH              | Subtract from high accumulator                               | 1       | 0   | 1   | 0    | 0    | 0    | 1   | 0    | 0          | ı   | 4   |    |     | - D-  |   |   | <b>→</b> |

| SUBK <sup>‡</sup> | Subtract from accumulator short immediate                    | 1       | 1   | 1   | 0    | 0    | 1    | 1   | 0    | 1          | •   |     |    | — k |       |   |   | <b>→</b> |

| SUBS              | Subtract from low accumulator with sign extension suppressed | 1       | 0   | 1   | 0    | 0    | 0    | 1   | 0    | 1          | ı   | 4   |    |     | - D-  |   |   | <b>→</b> |

$<sup>^{\</sup>dagger}$  These instructions are not included in the TMS320C1x instruction set.

<sup>&</sup>lt;sup>‡</sup> These instructions are not included in the TMS32020 instruction set.

Table 3. TMS320C25 Instruction Set Summary (continued)

|                             | ACCUMULATOR ME                                                                                                                                                                         | MORY RE      | FER                   | ENC              | E IN             | STRU             | ICTIO                            | ONS         |             |            |             |             |    |         |                          |             |      |                                       |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|------------------|------------------|------------------|----------------------------------|-------------|-------------|------------|-------------|-------------|----|---------|--------------------------|-------------|------|---------------------------------------|

| MNEMO                       | NIC DESCRIPTION                                                                                                                                                                        | NO.<br>WORDS |                       |                  |                  |                  | IN                               | STR         | UCT         | ION        | ВΙΊ         | гсс         | DE |         |                          |             |      |                                       |

|                             |                                                                                                                                                                                        | WONDO        | 15                    | 14               | 13               | 12               | 11                               | 10          | 9           | 8          | 7           | 6           | 5  | 4       | 3                        | 2           | 1    | 0                                     |

| SUBT†                       | Subtract from accumulator with shift specified by T register                                                                                                                           | 1            | 0                     | 1                | 0                | 0                | 0                                | 1           | 1           | 0          | ı           | •           |    |         | D-                       |             |      | <b>→</b>                              |

| XOR                         | Exclusive-OR with accumulator                                                                                                                                                          | 1            | 0                     | 1                | 0                | 0                | 1                                | 1           | 0           | 0          | I           | •           |    |         | D-                       |             |      | •                                     |

| XORK†                       | Exclusive-OR immediate with accumulator with shift                                                                                                                                     | 2            | 1                     | 1                | 0                | 1                | •                                | — s         | ; —         | -          | 0           | 0           | 0  | 0       | 0                        | 1           | 1    | 0                                     |

| ZAC                         | Zero accumulator                                                                                                                                                                       | 1            | 1                     | 1                | 0                | 0                | 1                                | 0           | 1           | 0          | 0           | 0           | 0  | 0       | 0                        | 0           | 0    | 0                                     |

| ZALH                        | Zero low accumulator and load high accumulator                                                                                                                                         | 1            | 0                     | 1                | 0                | 0                | 0                                | 0           | 0           | 0          | ı           | •           |    |         | D-                       |             |      | •                                     |

| ZALR‡                       | Zero low accumulator and load high accumulator with rounding                                                                                                                           | 1            | 0                     | 1                | 1                | 1                | 1                                | 0           | 1           | 1          | I           | •           |    |         | D-                       |             |      | <b>→</b>                              |

| ZALS                        | Zero accumulator and load low accumulator with sign extension suppressed                                                                                                               | 1            | 0                     | 1                | 0                | 0                | 0                                | 0           | 0           | 1          | I           | •           |    |         | D-                       |             |      | <b>→</b>                              |

|                             | AUXILIARY REGISTERS A                                                                                                                                                                  | ND DATA      | PAG                   | E PO             | TNIC             | ER IN            | ISTR                             | UCT         | ION         | IS         |             |             |    |         |                          |             |      |                                       |

| MNEMO                       | NIC DESCRIPTION                                                                                                                                                                        | NO.<br>WORDS |                       |                  |                  |                  | IN                               | STR         | UCT         | ION        | ВΙΊ         | гсс         | DE |         |                          |             |      |                                       |

|                             |                                                                                                                                                                                        | WONDO        | 15                    | 14               | 13               | 12               | 11                               | 10          | 9           | 8          | 7           | 6           | 5  | 4       | 3                        | 2           | 1    | 0                                     |

| ADRK‡                       | Add to auxiliary register short immediate                                                                                                                                              | 1            | 0                     | 1                | 1                | 1                | 1                                | 1           | 1           | 0          | •           | <del></del> |    | _       | K -                      |             |      | <b>→</b>                              |

| CMPR <sup>†</sup>           | Compare auxiliary register with auxiliary register AR0                                                                                                                                 | 1            | 1                     | 1                | 0                | 0                | 1                                | 1           | 1           | 0          | 0           | 1           | 0  | 1       | 0                        | 0           | F CN | /-▶                                   |

| LAR                         | Land audition, undistant                                                                                                                                                               | _            |                       |                  |                  |                  |                                  |             |             |            |             | _           |    |         | - D -                    |             |      | -▶                                    |

|                             | Load auxiliary register                                                                                                                                                                | 1            | 0                     | 0                | 1                | 1                | 0 ◀                              | <b>←</b>    | R           | -          |             | 4           |    |         | ט.                       |             |      | -                                     |

| LARK                        | Load auxillary register  Load auxilliary register short immediate                                                                                                                      | 1            | 0                     | 0                | 1                | 1                | 0 <b>4</b>                       | <b>←</b>    | R<br>R      | <b>→</b>   | '<br>•      | <b>-</b>    |    |         | - K                      |             |      | <b>.</b>                              |

|                             |                                                                                                                                                                                        |              | _                     | _                | -                | -                | 0 <b>4</b><br>0 <b>4</b>         | <b>←</b> 1  | • •         | <b>→</b> 1 | 1           | 0           | 0  | 0       | _                        | —<br>—      | R    | - <b>→</b>                            |

| LARK<br>LARP                | Load auxilliary register short immediate                                                                                                                                               | 1            | 1                     | 1                | 0                | 0                | 0 <                              | 1<br>0      | R           | 1<br>0     | 1<br>1      | 0           | 0  | 0       | _                        | —<br>—      | R    | →<br>→<br>→                           |

| LARK<br>LARP<br>LDP         | Load auxilliary register short immediate  Load auxilliary register pointer                                                                                                             | 1            | 1                     | 1                | 0                | 0                | 0 •                              | 1<br>0<br>0 | R           | 1 0        | 1<br>1      | 0           | 0  | 0<br>DP | - K<br>1 •<br>- D        | —<br>←<br>— | R    | →<br>→<br>→                           |

| LARK<br>LARP<br>LDP<br>LDPK | Load auxilliary register short immediate  Load auxilliary register pointer  Load data memory page pointer                                                                              | 1 1 1        | 1 0 0                 | 1 1 1            | 0 0              | 0 1 1            | 0 •                              | 0           | R           | •          | 1<br>1<br>0 | 0           | 0  |         | - K<br>1 •<br>- D        | 0           | R -  | • • • • • • • • • • • • • • • • • • • |

| LARK<br>LARP                | Load auxilliary register short immediate  Load auxilliary register pointer  Load data memory page pointer  Load data memory page pointer immediate                                     | 1 1 1 1      | 1<br>0<br>0           | 1<br>1<br>1<br>1 | 0 0 0            | 0<br>1<br>1<br>0 | 0 <b>4</b> 0 0 1                 | 0           | R<br>0<br>1 | •          | 1 I O I     | 4           |    | DP      | - K<br>1 •<br>- D        |             |      | • • • • • • • • • • • • • • • • • • • |

| LARK LARP LDP LDPK LRLK†    | Load auxilliary register short immediate Load auxilliary register pointer Load data memory page pointer Load data memory page pointer immediate Load auxiliary register long immediate | 1 1 1 1 2    | 1<br>0<br>0<br>1<br>1 | 1 1 1 1 1        | 0<br>0<br>0<br>0 | 0<br>1<br>1<br>0 | 0 <b>4</b> 0 <b>1</b> 0 <b>4</b> | 0           | R 0 1 0 R   | •          | 1 I O I     | 4           |    | DP      | - K<br>1 •<br>- D<br>• — |             |      | • • • • • • • • • • • • • • • • • • • |

$<sup>^{\</sup>dagger}$  These instructions are not included in the TMS320C1x instruction set.

$<sup>^{\</sup>ddagger}$  These instructions are not included in the TMS32020 instruction set.

Table 3. TMS320C25 Instruction Set Summary (continued)

|                   | T REGISTER, P REGIS                                         | STER, AN     | D MU | JLTIF | PLY I | NSTF | RUCT | TION: | s   |     |     |     |    |   |       |     |             |          |

|-------------------|-------------------------------------------------------------|--------------|------|-------|-------|------|------|-------|-----|-----|-----|-----|----|---|-------|-----|-------------|----------|

| MNEMO             | NIC DESCRIPTION                                             | NO.<br>WORDS |      |       |       |      | IN   | STR   | UCT | ION | ВІТ | гсс | DE |   |       |     |             |          |

|                   |                                                             |              | 15   | 14    | 13    | 12   | 11   | 10    | 9   | 8   | 7   | 6   | 5  | 4 | 3     | 2   | 1           | 0        |

| APAC              | Add P register to accumulator                               | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 1 | 0     | 1   | 0           | 1        |

| LPH <sup>†</sup>  | Load high P register                                        | 1            | 0    | 1     | 0     | 1    | 0    | 0     | 1   | 1   | I   | •   |    |   | - D   |     |             | <b>→</b> |

| LT                | Load T register                                             | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 0   | 0   | I   | •   |    |   | - D - |     |             | <b>→</b> |

| LTA               | Load T register and accumulate previous product             | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 0   | 1   | I   | •   |    |   | - D - |     |             | <b>→</b> |

| LTD               | Load T register, accumulate previous product, and move data | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 1   | 1   | ı   | 4   |    |   | - D   |     |             | <b>→</b> |

| LTP <sup>†</sup>  | Load T register and store P register in accumulator         | 1            | 0    | 0     | 1     | 1    | 1    | 1     | 1   | 0   | I   | 4   |    |   | - D   |     |             | <b>→</b> |

| LTS†              | Load T register and subtract previous product               | 1            | 0    | 1     | 0     | 1    | 1    | 0     | 1   | 1   | 1   | 4   |    |   | - D - |     |             | <b>→</b> |

| MAC <sup>†</sup>  | Multiply and accumulate                                     | 2            | 0    | 1     | 0     | 1    | 1    | 1     | 0   | 1   | 1   | 4   |    |   | - D - |     |             | <b>→</b> |

| MACD <sup>†</sup> | Multiply and accumulate with data move                      | 2            | 0    | 1     | 0     | 1    | 1    | 1     | 0   | 0   | 1   | 4   |    |   | - D - |     |             | <b>→</b> |

| MPY               | Multiply (with T register, store product in P register)     | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 0   | 0   | ı   | 4   |    |   | - D   |     |             | <b>→</b> |

| MPYA <sup>‡</sup> | Multiply and accumulate previous product                    | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 1   | 0   | I   | 4   |    |   | - D - |     |             | <b>-</b> |

| MPYK              | Multiply immediate                                          | 1            | 1    | 0     | 1     | •    |      |       |     |     | _   | K - |    |   |       |     |             | <b>→</b> |

| MPYS‡             | Multiply and subtract previous product                      | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 1   | 1   | 1   | 4   |    |   | - D - |     |             | <b>→</b> |

| MPYU‡             | Multiply unsigned                                           | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 1   | I   | 4   |    |   | - D - |     |             | <b>→</b> |

| PAC               | Load accumulator with P register                            | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 1 | 0     | 1   | 0           | 0        |

| SPAC              | Subtract P register from accumulator                        | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 1 | 0     | 1   | 1           | 0        |

| SPH‡              | Store high P register                                       | 1            | 0    | 1     | 1     | 1    | 1    | 1     | 0   | 1   | 1   | 4   |    |   | - D - |     |             | <b>-</b> |

| SPL <sup>‡</sup>  | Store low P register                                        | 1            | 0    | 1     | 1     | 1    | 1    | 1     | 0   | 0   | 1   | 4   |    |   | - D - |     |             | <b>-</b> |

| SPM <sup>†</sup>  | Set P register output shift mode                            | 1            | 1    | 1     | 0     | 0    | 1    | 1     | 1   | 0   | 0   | 0   | 0  | 0 | 1     | 0 • | <b>◆</b> PI | MÞ       |

| SQRA <sup>†</sup> | Square and accumulate                                       | 1            | 0    | 0     | 1     | 1    | 1    | 0     | 0   | 1   | ı   | 4   |    |   | - D - |     |             | <b>→</b> |

| SQRS†             | Square and subtract previous product                        | 1            | 0    | 1     | 0     | 1    | 1    | 0     | 1   | 0   | ı   | 4   |    |   | - D   |     |             | ->       |

<sup>&</sup>lt;sup>†</sup> These instructions are not included in the TMS320C1x instruction set.

<sup>&</sup>lt;sup>‡</sup> These instructions are not included in the TMS32020 instruction set.

Table 3. TMS320C25 Instruction Set Summary (continued)

|                                                                                          | BRAN                                                                                         | ICH/CALL     | INO         | HUC         | ,1101       | NS          |        |        |             |          |     |      |                  |             |             |                  |             |            |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------|-------------|-------------|-------------|-------------|--------|--------|-------------|----------|-----|------|------------------|-------------|-------------|------------------|-------------|------------|

| MNEMO                                                                                    | ONIC DESCRIPTION                                                                             | NO.          |             |             |             |             | I      | NSTI   | RUC         | CIT      | N B | IT C | ODI              | E           |             |                  |             |            |

|                                                                                          |                                                                                              | Wonbo        | 15          | 14          | 13          | 12          | 11     | 10     | 9           | 8        | 7   | 6    | 5                | 4           | 3           | 2                | 1           | C          |

| В                                                                                        | Branch unconditionally                                                                       | 2            | 1           | 1           | 1           | 1           | 1      | 1      | 1           | 1        | 1   | •    | •                |             | — c         | ) —              |             | -          |

| BACC†                                                                                    | Branch to address specified by accumulator                                                   | 1            | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 1                | 0           | 0           | 1                | 0           | •          |

| BANZ                                                                                     | Branch on auxiliary register not zero                                                        | 2            | 1           | 1           | 1           | 1           | 1      | 0      | 1           | 1        | 1   | •    | •                |             | — c         | ) —              |             | -1         |

| BBNZ†                                                                                    | Branch if TC bit ≠ 0                                                                         | 2            | 1           | 1           | 1           | 1           | 1      | 0      | 0           | 1        | 1   | •    | •                |             | — с         | <b>—</b>         |             | -          |

| BBZ†                                                                                     | Branch if TC bit = 0                                                                         | 2            | 1           | 1           | 1           | 1           | 1      | 0      | 0           | 0        | 1   | •    | •                |             | — c         | ) —              |             | -          |

| BC <sup>‡</sup>                                                                          | Branch on carry                                                                              | 2            | 0           | 1           | 0           | 1           | 1      | 1      | 1           | 0        | 1   | •    | <b>←</b>         |             | — с         | <b>—</b>         |             | -1         |

| BGEZ                                                                                     | Branch if accumulator ≥ 0                                                                    | 2            | 1           | 1           | 1           | 1           | 0      | 1      | 0           | 0        | 1   | •    | •                |             | — c         | <b>—</b>         |             | -          |

| BGZ                                                                                      | Branch if accumulator > 0                                                                    | 2            | 1           | 1           | 1           | 1           | 0      | 0      | 0           | 1        | 1   | •    | <b>←</b>         |             | — с         | ) —              |             | <b>—</b> 1 |

| BIOZ                                                                                     | Branch on I/O status = 0                                                                     | 2            | 1           | 1           | 1           | 1           | 1      | 0      | 1           | 0        | 1   | •    | <b>←</b>         |             | — с         | <b>)</b> —       |             | -          |

| BLEZ                                                                                     | Branch if accumulator ≤ 0                                                                    | 2            | 1           | 1           | 1           | 1           | 0      | 0      | 1           | 0        | 1   | •    | <b>←</b>         |             | — с         | <b>)</b> —       |             | -1         |

| BLZ                                                                                      | Branch if accumulator < 0                                                                    | 2            | 1           | 1           | 1           | 1           | 0      | 0      | 1           | 1        | 1   | •    | <b>←</b>         |             | — с         | <b>)</b> —       |             | -          |

| BNC‡                                                                                     | Branch on no carry                                                                           | 2            | 0           | 1           | 0           | 1           | 1      | 1      | 1           | 1        | 1   |      | <b>←</b>         |             | — c         | <b>)</b> —       |             |            |

| BNV <sup>†</sup>                                                                         | Branch if no overflow                                                                        | 2            | 1           | 1           | 1           | 1           | 0      | 1      | 1           | 1        | 1   | •    | <u> </u>         |             | — с         | <b>)</b> —       |             |            |

| BNZ                                                                                      | Branch if accumulator ≠ 0                                                                    | 2            | 1           | 1           | 1           | 1           | 0      | 1      | 0           | 1        | 1   |      | •                |             | — c         | ) —              |             | _          |

| BV                                                                                       | Branch on overflow                                                                           | 2            | 1           | 1           | 1           | 1           | 0      | 0      | 0           | 0        | 1   |      | ·<br>—           |             | — c         |                  |             |            |

| BZ                                                                                       | Branch if accumulator = 0                                                                    | 2            | 1           | 1           | 1           | 1           | 0      | 1      | 1           | 0        | 1   | •    | <u>`</u>         |             | — c         |                  |             |            |

| CALA                                                                                     | Call subroutine indirect                                                                     | 1 1          | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 1                | 0           | 0           | 1                | 0           | (          |

| CALL                                                                                     | Call subroutine                                                                              | 2            | 1           | 1           | 1           | 1           | 1      | 1      | 1           | 0        | 1   | •    | •                |             | — c         |                  |             |            |

| RET                                                                                      | Return from subroutine                                                                       | 1 1          | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 1                | 0           | 0           | 1                | 1           |            |

|                                                                                          |                                                                                              | DATA MEN     | -           | -           |             |             | s<br>S |        | •           |          |     |      | •                |             | _           | •                |             |            |

|                                                                                          |                                                                                              |              |             |             |             |             |        | NSTI   | חור         | חדי      | M P | IT C | יחסי             |             |             |                  |             |            |

| MNEMC                                                                                    | DNIC DESCRIPTION                                                                             | NO.<br>WORDS |             |             |             |             |        |        |             |          |     |      |                  |             |             | _                |             |            |

| BLKD†                                                                                    | Block move from data memory to data memory                                                   | 2            | 15<br>1     | 14          | 13<br>1     | <b>12</b>   | 11     | 10     | <b>9</b>    | 8<br>1   | 7   | 6    | 5                | 4           | 3           |                  | 1           |            |

|                                                                                          | Block move from program memory to data                                                       |              |             |             |             |             |        | '      |             |          |     | •    |                  |             | — C         | , —              |             |            |

| BLKP <sup>†</sup>                                                                        | memory                                                                                       | 2            | 1           | 1           | 1           | 1           | 1      | 1      | 0           | 0        | I   | •    | •                |             | — C         | ) —              |             |            |

| DMOV                                                                                     | Data move in data memory                                                                     | 1            | 0           | 1           | 0           | 1           | 0      | 1      | 1           | 0        | I   | •    | •                |             | — с         | <b>—</b>         |             |            |

| FORT†                                                                                    | Format serial port registers                                                                 | 1            | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 0                | 0           | 1           | 1                | 1           | F          |

| IN                                                                                       | Input data from port                                                                         | 1            | 1           | 0           | 0           | 0           | •      |        | PA          | <b>—</b> | ▶ I | •    | •                |             | — с         | <b>—</b>         |             |            |

| OUT                                                                                      | Output data to port                                                                          | 1            | 1           | 1           | 1           | 0           | •      |        | PA          | <b>—</b> | νI  | •    | <b>←</b>         |             | — с         | <b>)</b> —       |             |            |

| 001                                                                                      | Reset serial port frame synchronization mode                                                 | 1            | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 1                | 1           | 0           | 1                | 1           |            |

|                                                                                          |                                                                                              | 1 .          |             | 4           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 1                | 0           | ^           | 0                | 0           |            |

| RFSM <sup>‡</sup>                                                                        | Reset serial port transmit mode                                                              | 1            | 1           | 1           | U           | •           |        |        |             |          |     |      |                  | •           | 0           | U                | -           |            |

| RFSM <sup>‡</sup><br>RTXM <sup>†</sup>                                                   | Reset serial port transmit mode Reset external flag                                          | 1            | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 0                | 0           | 1           | 1                | 0           |            |

| RFSM <sup>‡</sup><br>RTXM <sup>†</sup><br>RXF <sup>†</sup>                               | ·                                                                                            |              |             |             |             |             | 1      | 1<br>1 | 1           | 0        | 0   | 0    | 0                |             |             |                  |             |            |

| RFSM <sup>‡</sup> RTXM <sup>†</sup> RXF <sup>†</sup> SFSM <sup>‡</sup> STXM <sup>†</sup> | Reset external flag                                                                          | 1            | 1           | 1           | 0           | 0           | -      |        | 1<br>1<br>1 |          |     |      | 0<br>1<br>1      |             | 1           | 1                | 0           |            |

| RFSM <sup>‡</sup><br>RTXM <sup>†</sup><br>RXF <sup>†</sup><br>SFSM <sup>‡</sup>          | Reset external flag Set serial port frame synchronization mode                               | 1 1          | 1           | 1           | 0           | 0           | 1      | 1      | 1           | 0        | 0   | 0    | 0<br>1<br>1<br>0 | 0           | 1           | 1                | 0           |            |

| RFSM <sup>‡</sup> RTXM <sup>†</sup> RXF <sup>†</sup> SFSM <sup>‡</sup> STXM <sup>†</sup> | Reset external flag Set serial port frame synchronization mode Set serial port transmit mode | 1<br>1<br>1  | 1<br>1<br>1 | 1<br>1<br>1 | 0<br>0<br>0 | 0<br>0<br>0 | 1      | 1<br>1 | 1           | 0        | 0   | 0    | 1                | 0<br>1<br>0 | 1<br>0<br>0 | 1<br>1<br>0<br>1 | 0<br>1<br>0 |            |

$<sup>^{\</sup>dagger}$  These instructions are not included in the TMS320C1x instruction set.

<sup>&</sup>lt;sup>‡</sup> These instructions are not included in the TMS32020 instruction set.

Table 3. TMS320C25 Instruction Set Summary (concluded)

|                   | CON                                                  | TROL INS | TRU                                                           | СТІО | NS |    |          |     |     |          |    |   |   |     |       |   |   |          |

|-------------------|------------------------------------------------------|----------|---------------------------------------------------------------|------|----|----|----------|-----|-----|----------|----|---|---|-----|-------|---|---|----------|

| MNEMONIC          | DESCRIPTION                                          | NO.      | NO. INSTRUCTION BIT CODE  15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 |      |    |    |          |     |     |          |    |   |   |     |       |   |   |          |

|                   |                                                      | WORDS    | 15                                                            | 14   | 13 | 12 | 11       | 10  | 9   | 8        | 7  | 6 | 5 | 4   | 3     | 2 | 1 | 0        |

| BIT <sup>†</sup>  | Test bit                                             | 1        | 1                                                             | 0    | 0  | 1  | <b>+</b> | — Е | 3 — | <b>-</b> | I  | + |   |     | - D - |   |   | <b>→</b> |

| BITT <sup>†</sup> | Test bit specified by T register                     | 1        | 0                                                             | 1    | 0  | 1  | 0        | 1   | 1   | 1        | -1 | • |   |     | - D - |   |   | <b>→</b> |

| CNFD <sup>†</sup> | Configure block as data memory                       | 1        | 1                                                             | 1    | 0  | 0  | 1        | 1   | 1   | 0        | 0  | 0 | 0 | 0   | 0     | 1 | 0 | 0        |

| CNFP <sup>†</sup> | Configure block as program memory                    | 1        | 1                                                             | 1    | 0  | 0  | 1        | 1   | 1   | 0        | 0  | 0 | 0 | 0   | 0     | 1 | 0 | 1        |

| DINT              | Disable interrupt                                    | 1        | 1                                                             | 1    | 0  | 0  | 1        | 1   | 1   | 0        | 0  | 0 | 0 | 0   | 0     | 0 | 0 | 1        |

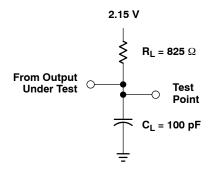

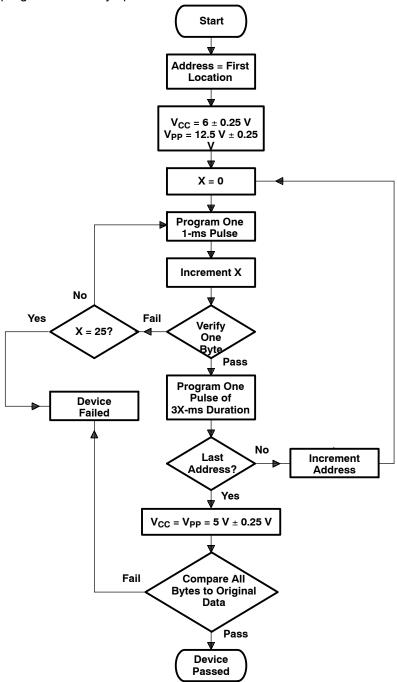

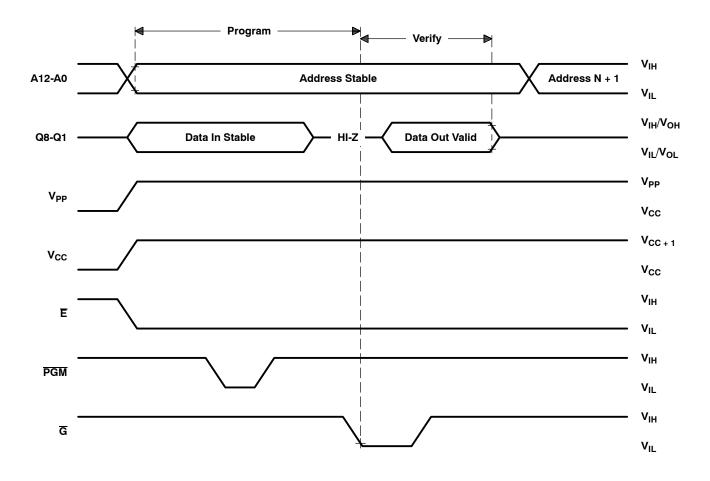

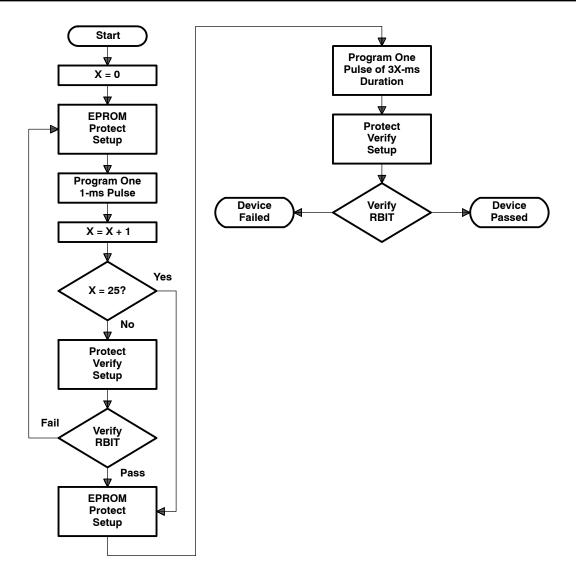

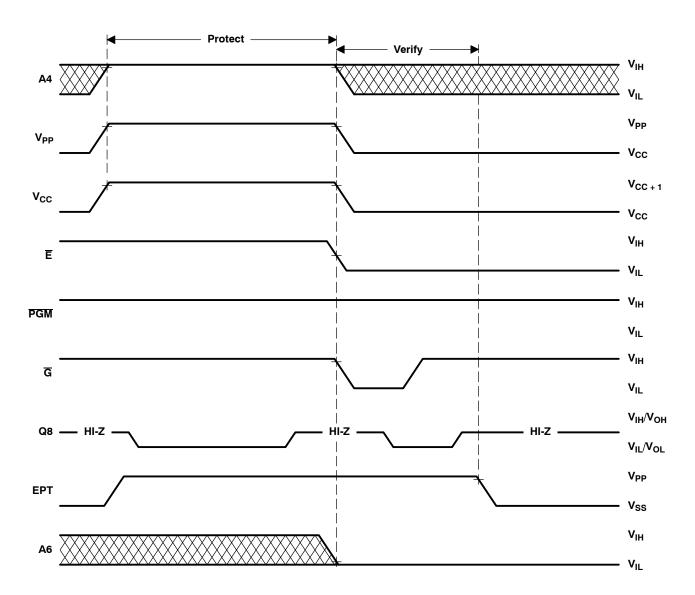

| EINT              | Enable interrupt                                     | 1        | 1                                                             | 1    | 0  | 0  | 1        | 1   | 1   | 0        | 0  | 0 | 0 | 0   | 0     | 0 | 0 | 0        |