SPRS645F-AUGUST 2010-REVISED OCTOBER 2013

# TMS320C5515 Fixed-Point Digital Signal Processor

Check for Samples: TMS320C5515

#### **Fixed-Point Digital Signal Processor** 1

#### **Features** 1.1

- High-Performance, Low-Power, TMS320C55x™ **Fixed-Point Digital Signal Processor**

- 16.67-, 13.33-, 10-, 8.33-ns Instruction Cycle Time

- 60-, 75-, 100-, 120-MHz Clock Rate

- One/Two Instructions Executed per Cycle

- Dual Multipliers [Up to 200 or 240 Million Multiply-Accumulates per Second (MMACS)]

- Two Arithmetic/Logic Units (ALUs)

- Three Internal Data/Operand Read Buses and Two Internal Data/Operand Write Buses

- Software-Compatible With C55x Devices

- Industrial Temperature Devices Available

- 320K Bytes Zero-Wait State On-Chip RAM, Composed of:

- 64K Bytes of Dual-Access RAM (DARAM), 8 Blocks of 4K x 16-Bit

- 256K Bytes of Single-Access RAM (SARAM), 32 Blocks of 4K x 16-Bit

- 128K Bytes of Zero Wait-State On-Chip ROM (4 Blocks of 16K x 16-Bit)

- 4M x 16-Bit Maximum Addressable External Memory Space (SDRAM/mSDRAM)

- 16-/8-Bit External Memory Interface (EMIF) with ٠ **Glueless Interface to:**

- 8-/16-Bit NAND Flash, 1- and 4-Bit ECC

- 8-/16-Bit NOR Flash

- Asynchronous Static RAM (SRAM)

- SDRAM/mSDRAM (1.8-, 2.5-, 2.75-, and 3.3-V)

- Direct Memory Access (DMA) Controller

- Four DMA With 4 Channels Each (16-Channels Total)

- Three 32-Bit General-Purpose Timers One Selectable as a Watchdog and/or GP

- Two MultiMedia Card/Secure Digital (MMC/SD) Interfaces

- **Universal Asynchronous Receiver/Transmitter** (UART)

- Serial-Port Interface (SPI) With Four Chip-Selects

- Master/Slave Inter-Integrated Circuit (I<sup>2</sup>C Bus<sup>™</sup>)

- Four Inter-IC Sound (I<sup>2</sup>S Bus<sup>™</sup>) for Data Transport

- Device USB Port With Integrated 2.0 High-Speed PHY that Supports:

- USB 2.0 Full- and High-Speed Device

- LCD Bridge With Asynchronous Interface

- **Tightly-Coupled FFT Hardware Accelerator** ٠

- 10-Bit 4-Input Successive Approximation (SAR) • ADC

- Real-Time Clock (RTC) With Crystal Input, With Separate Clock Domain and Power Supply

- Four Core Isolated Power Supply Domains: Analog, RTC, CPU and Peripherals, and USB

- Four I/O Isolated Power Supply Domains: RTC I/O, EMIF I/O, USB PHY, and DV<sub>DDIO</sub>

- Three integrated LDOs (DSP LDO, ANA LDO, and USB\_LDO) to power the isolated domains: DSP Core, Analog, and USB Core, respectively

- Low-Power S/W Programmable Phase-Locked Loop (PLL) Clock Generator

- On-Chip ROM Bootloader (RBL) to Boot From NAND Flash, NOR Flash, SPI EEPROM, SPI Serial Flash or I2C EEPROM

- IEEE-1149.1 (JTAG) **Boundary-Scan-Compatible**

- Up to 26 General-Purpose I/O (GPIO) Pins (Multiplexed With Other Device Functions)

- 196-Terminal Pb-Free Plastic BGA (Ball Grid Array) (ZCH Suffix)

- 1.05-V Core (60 or 75 MHz), 1.8-V, 2.5-V, 2.75-V, or 3.3-V I/Os

- 1.3-V Core (100, 120 MHz), 1.8-V, 2.5-V, 2.75-V, or 3.3-V I/Os

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. All trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SPRS645F-AUGUST 2010-REVISED OCTOBER 2013

www.ti.com

# 1.2 Applications

- Wireless Audio Devices (Headsets, Microphones, Speakerphones)

- Echo Cancellation Headphones

- Portable Medical Devices

- Voice Applications

- Industrial Controls

- Fingerprint Biometrics

- Software Defined Radio

# 1.3 Description

The device is a member of TI's TMS320C5000<sup>™</sup> fixed-point Digital Signal Processor (DSP) product family and is designed for low-power applications.

The fixed-point DSP is based on the TMS320C55x<sup>™</sup> DSP generation CPU processor core. The C55x<sup>™</sup> DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32-bit data read bus and two 16-bit data read buses, two 16-bit data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to four 16-bit data reads and two 16-bit data writes in a single cycle. The device also includes four DMA controllers, each with 4 channels, providing data movement for 16-independent channel contexts without CPU intervention. Each DMA controller can perform one 32-bit data transfer per cycle, in parallel and independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication and a 32-bit add in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x CPU supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to the Address Unit (AU) and Data Unit (DU) resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instructions.

The general-purpose input and output functions along with the 10-bit SAR ADC provide sufficient pins for status, interrupts, and bit I/O for LCD displays, keyboards, and media interfaces. Serial media is supported through two MultiMedia Card/Secure Digital (MMC/SD) peripherals, four Inter-IC Sound (I2S Bus<sup>™</sup>) modules, one Serial-Port Interface (SPI) with up to 4 chip selects, one I2C multi-master and slave interface, and a Universal Asynchronous Receiver/Transmitter (UART) interface.

The device peripheral set includes an external memory interface (EMIF) that provides glueless access to asynchronous memories like EPROM, NOR, NAND, and SRAM, as well as to high-speed, high-density memories such as synchronous DRAM (SDRAM) and mobile SDRAM (mSDRAM). Additional peripherals include: a high-speed Universal Serial Bus (USB2.0) device mode only, and a real-time clock (RTC). This device also includes three general-purpose timers with one configurable as a watchdog timer, and an analog phase-locked loop (APLL) clock generator.

In addition, the device includes a tightly-coupled FFT Hardware Accelerator. The tightly-coupled FFT Hardware Accelerator supports 8 to 1024-point (in power of 2) real and complex-valued FFTs.

2

SPRS645F-AUGUST 2010-REVISED OCTOBER 2013

Furthermore, the device includes three integrated LDOs (DSP\_LDO, ANA\_LDO, and USB\_LDO) to power different sections of the device. The DSP\_LDO can provide 1.3 V or 1.05 V to the DSP core ( $CV_{DD}$ ), selectable on-the-fly by software as long as operating frequency ranges are observed. To allow for lowest power operation, the programmer can shutdown the internal DSP\_LDO cutting power to the DSP core ( $CV_{DD}$ ) while an external supply provides power to the RTC ( $CV_{DDRTC}$  and  $DV_{DDRTC}$ ). The ANA\_LDO is designed to provide 1.3 V to the DSP PLL ( $V_{DDA_{PLL}}$ ), SAR, and power management circuits ( $V_{DDA_{ANA}}$ ). The USB\_LDO provides 1.3 V to USB core digital (USB\_ $V_{DD1P3}$ ) and PHY circuits (USB\_ $V_{DDA1P3}$ ). The RTC alarm interrupt or the WAKEUP pin can re-enable the internal DSP\_LDO and re-apply power to the DSP core.

The device is supported by the industry's award-winning eXpressDSP<sup>™</sup>, Code Composer Studio<sup>™</sup> Integrated Development Environment (IDE), DSP/BIOS<sup>™</sup>, Texas Instruments' algorithm standard, and the industry's largest third-party network. Code Composer Studio IDE features code generation tools including a C Compiler and Linker, RTDX<sup>™</sup>, XDS100<sup>™</sup>, XDS510<sup>™</sup>, XDS560<sup>™</sup> emulation device drivers, and evaluation modules. The device is also supported by the C55x DSP Library which features more than 50 foundational software kernels (FIR filters, IIR filters, FFTs, and various math functions) as well as chip support libraries.

SPRS645F-AUGUST 2010-REVISED OCTOBER 2013

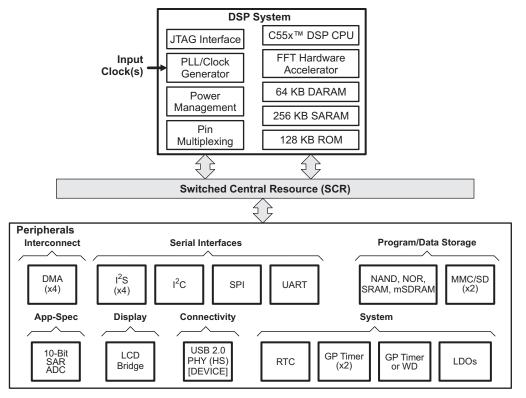

# 1.4 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the device.

Figure 1-1. Functional Block Diagram

4

www.ti.com

# TMS320C5515

# TEXAS INSTRUMENTS

#### www.ti.com

| 1   | Fixed  | d-Point Digital Signal Processor                                                      | . <u>1</u> |

|-----|--------|---------------------------------------------------------------------------------------|------------|

|     | 1.1    | Features                                                                              | _          |

|     | 1.2    | Applications                                                                          |            |

|     | 1.3    | Description                                                                           | <u>2</u>   |

|     | 1.4    | Functional Block Diagram                                                              | . 4        |

| Rev | ision/ | History                                                                               |            |

| 2   | Devi   | ce Overview                                                                           | <u>7</u>   |

|     | 2.1    | Device Characteristics                                                                | . 7        |

|     | 2.2    | C55x CPU                                                                              | <u>9</u>   |

|     | 2.3    | Memory Map Summary                                                                    | <u>13</u>  |

|     | 2.4    | Pin Assignments                                                                       | <u>14</u>  |

|     | 2.5    | Terminal Functions                                                                    | <u>15</u>  |

| 3   | Devi   | ce Configuration                                                                      | <u>48</u>  |

|     | 3.1    | System Registers                                                                      | <u>48</u>  |

|     | 3.2    | Power Considerations                                                                  | <u>49</u>  |

|     | 3.3    | Clock Considerations                                                                  | <u>52</u>  |

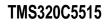

|     | 3.4    | Boot Sequence                                                                         | <u>54</u>  |

|     | 3.5    | Configurations at Reset                                                               | <u>57</u>  |

|     | 3.6    | Configurations After Reset                                                            | <u>58</u>  |

|     | 3.7    | Multiplexed Pin Configurations                                                        | <u>61</u>  |

|     | 3.8    | Debugging Considerations                                                              | <u>65</u>  |

| 4   | Devi   | ce Operating Conditions                                                               | <u>67</u>  |

|     | 4.1    | Absolute Maximum Ratings Over Operating Case                                          |            |

|     |        | Temperature Range (Unless Otherwise Noted)                                            | <u>67</u>  |

|     | 4.2    | Recommended Operating Conditions                                                      | <u>68</u>  |

|     | 4.3    | Electrical Characteristics Over Recommended<br>Ranges of Supply Voltage and Operating |            |

|     |        | Temperature (Unless Otherwise Noted)                                                  | 69         |

| 5   | Perip  | oheral Information and Electrical                                                     | _          |

|     |        | ifications                                                                            | <u>72</u>  |

|     | 5.1    | Parameter Information                                                                 | <u>72</u>  |

| _   |        |                                                                                       |            |

#### SPRS645F-AUGUST 2010-REVISED OCTOBER 2013

| 5.2   | Recommended Clock and Control Signal Transition<br>Behavior                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.3   | Power Supplies                                                                                                                                                                                              | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5.4   | External Clock Input From RTC_XI, CLKIN, and USB_MXI Pins                                                                                                                                                   | <u>76</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.5   | Clock PLLs                                                                                                                                                                                                  | <u>80</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.6   | Direct Memory Access (DMA) Controller                                                                                                                                                                       | <u>82</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.7   | Reset                                                                                                                                                                                                       | <u>83</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.8   | Wake-up Events, Interrupts, and XF                                                                                                                                                                          | <u>87</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.9   | External Memory Interface (EMIF)                                                                                                                                                                            | <u>89</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5.10  | Multimedia Card/Secure Digital (MMC/SD)                                                                                                                                                                     | <u>103</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.11  | Real-Time Clock (RTC)                                                                                                                                                                                       | 108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.12  | Inter-Integrated Circuit (I2C)                                                                                                                                                                              | <u>112</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.13  | Universal Asynchronous Receiver/Transmitter (UART)                                                                                                                                                          | 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.14  | Inter-IC Sound (I2S)                                                                                                                                                                                        | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.15  | Liquid Crystal Display Controller (LCDC)                                                                                                                                                                    | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.16  | 10-Bit SAR ADC                                                                                                                                                                                              | 134                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.17  | Serial Port Interface (SPI)                                                                                                                                                                                 | 135                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.18  | Universal Serial Bus (USB) 2.0 Controller                                                                                                                                                                   | 138                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.19  | General-Purpose Timers                                                                                                                                                                                      | <u>145</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.20  | General-Purpose Input/Output                                                                                                                                                                                | <u>147</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5.21  | IEEE 1149.1 JTAG                                                                                                                                                                                            | <u>151</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Devic | e and Documentation Support                                                                                                                                                                                 | <u>153</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.1   | Device Support                                                                                                                                                                                              | <u>153</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 6.2   | Community Resources                                                                                                                                                                                         | <u>154</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|       |                                                                                                                                                                                                             | <u>155</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       |                                                                                                                                                                                                             | <u>155</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

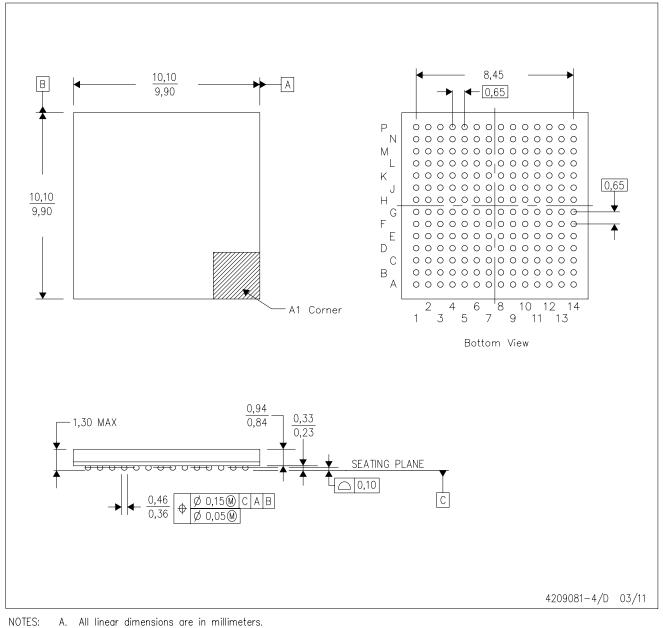

| 7.2   | Packaging Information                                                                                                                                                                                       | <u>155</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|       | 5.3<br>5.4<br>5.5<br>5.6<br>5.7<br>5.8<br>5.9<br>5.10<br>5.11<br>5.12<br>5.13<br>5.14<br>5.15<br>5.16<br>5.17<br>5.18<br>5.19<br>5.20<br>5.21<br><b>Devic</b><br>6.1<br>6.2<br><b>Mech</b><br>Inform<br>7.1 | Behavior       S.3         5.3       Power Supplies         5.4       External Clock Input From RTC_XI, CLKIN, and USB_MXI Pins         5.5       Clock PLLs         5.6       Direct Memory Access (DMA) Controller         5.7       Reset         5.8       Wake-up Events, Interrupts, and XF         5.9       External Memory Interface (EMIF)         5.10       Multimedia Card/Secure Digital (MMC/SD)         5.11       Real-Time Clock (RTC)         5.12       Inter-Integrated Circuit (I2C)         5.13       Universal Asynchronous Receiver/Transmitter (UART)         5.14       Inter-IC Sound (I2S)         5.15       Liquid Crystal Display Controller (LCDC)         5.16       10-Bit SAR ADC         5.17       Serial Port Interface (SPI)         5.18       Universal Serial Bus (USB) 2.0 Controller         5.19       General-Purpose Timers         5.20       General-Purpose Input/Output         5.21       IEEE 1149.1 JTAG         Device and Documentation Support         6.1       Device Support         6.2       Community Resources         Mechanical Packaging and Orderable         Information         7.1       Thermal Data for ZCH |

6

7

SPRS645F-AUGUST 2010-REVISED OCTOBER 2013

### **Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

This data manual revision history highlights the technical changes made to the document.

**Scope:** Applicable updates to the TMS320C5000 device family, specifically relating to the device (Silicon Revisions 2.0) which is now in the production data (PD) stage of development have been incorporated.

| SEE                                         | ADDITIONS/MODIFICATIONS/DELETIONS                                                                                                                                                    |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Global                                      | <ul> <li>Added notes to clarify that CV<sub>DDRTC</sub> must always be powered by an external power supply and<br/>none of the on-chip LDOs can power CV<sub>DDRTC</sub>.</li> </ul> |

| Section 2                                   | Table 2-1, Characteristics of the C5515 Processor.                                                                                                                                   |

| Device Overview                             | Deleted Power Characterization                                                                                                                                                       |

|                                             | <ul> <li>Updated addresses for MMC/SD0 and MMC/SD1 in Table 2-4, Peripheral I/O-Space Control<br/>Registers.</li> </ul>                                                              |

| Section 2.5                                 | Table 2-7, RESET, Interrupts, and JTAG Terminal Functions:                                                                                                                           |

| Ferminal Functions                          | Deleted duplicate note on board design guidelines.                                                                                                                                   |

|                                             | Table 2-8, External Memory Interface (EMIF) Terminal Functions:                                                                                                                      |

|                                             | • Changed note for 16-bit asynchronous memory to connect EM_A[20:0] to memory address pins [21:1].                                                                                   |

|                                             | Table 2-13, USB2.0 Terminal Functions                                                                                                                                                |

|                                             | • Added power-on information for USB_VBUS, USB_V <sub>DDA3P3</sub> , USB_V <sub>DDA1P3</sub> , and USB_V <sub>DD1P3</sub> .                                                          |

|                                             | Table 2-20, Reserved and No Connects Terminal Functions:                                                                                                                             |

|                                             | Updated RSV16 description to tie directly to V <sub>SS</sub> .                                                                                                                       |

| Section 3                                   | Added note stating Device ID registers are reserved.                                                                                                                                 |

| Device Configuration                        | Updated reset value for WU_DOUT from 0 to 1.                                                                                                                                         |

|                                             | Section 3.4, Boot Sequence:                                                                                                                                                          |

|                                             | Added steps to set register configuration and copy boot image sections (steps 15 and 16).                                                                                            |

|                                             | Changed Figure 3-2, Bootloader Software Architecture.                                                                                                                                |

|                                             | Added reset default to pin multiplexing tables.                                                                                                                                      |

| Section 4                                   | Section 4.3                                                                                                                                                                          |

| Device Operating<br>Conditions              | Added note for core (CV <sub>DD</sub> ) supply power (P).                                                                                                                            |

|                                             | Updated ESD Stress Voltage value for HBM to > 1000 V and CDM to > 250 V.                                                                                                             |

| Section 5.3<br>Power Supplies               | Updated Section 5.3.1, Power-Supply Sequencing.                                                                                                                                      |

| Section 5.5.1                               | Table 5-3, PLL Clock Frequency Ranges:                                                                                                                                               |

| PLL Device-Specific<br>Information          | Updated maximum value for PLL_LOCKTIME.                                                                                                                                              |

| Section 5.8.2                               | Table 5-8, Timing Requirements for Wake-Up From IDLE:                                                                                                                                |

| Wake-Up From IDLE<br>Electrical Data/Timing | <ul> <li>Changed minimum value to 30.5 µs from 10 ns.</li> </ul>                                                                                                                     |

|                                             | Table 5-9, Switching Characteristics Over Recommended Operating Conditions For Wake-Up From IDLE:                                                                                    |

|                                             | Changed parameter description to, "Delay time, WAKEUP pulse complete to CPU active."                                                                                                 |

|                                             | • Moved 2 to WAKEUP pulse complete from wake-up event high in Figure 5-14, Wake-Up From IDLE Timings.                                                                                |

| Section 5.9                                 | Global:                                                                                                                                                                              |

| External Memory                             | • Updated device limitations on EM_SDCLK when DV <sub>DDEMIF</sub> = 1.8 V and 1.3 V.                                                                                                |

| Interface (EMIF)                            | Added notes to timing and switching tables.                                                                                                                                          |

| Section 5.11<br>Real-Time Clock (RTC)       | • Added to wake-up sequence in Section 5.11.1, RTC Only Mode.                                                                                                                        |

| Section 6                                   | Moved documentation support to Section 7 from Section 3.6 and 3.7.                                                                                                                   |

| Device and                                  |                                                                                                                                                                                      |

| Documentation Support                       |                                                                                                                                                                                      |

# 2 Device Overview

## 2.1 Device Characteristics

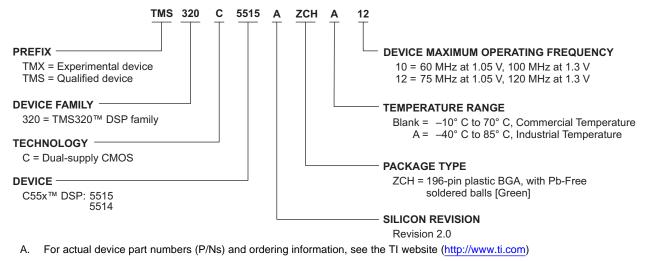

Table 2-1, provides an overview of the TMS320C5515 DSP. The tables show significant features of the device, including the capacity of on-chip RAM, the peripherals, the CPU frequency, and the package type with pin count. For more detailed information on the actual device part number and maximum device operating frequency, see Section 6.1.2, *Device and Development-Support Tool Nomenclature*.

| HA                                                                       | RDWARE FEATURES                            | C5515             |                                                                                                                                                            |  |  |  |  |

|--------------------------------------------------------------------------|--------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Peripherals<br>Not all peripheral pins are<br>available at the same time | External Memory Interface                  | e (EMIF)          | Asynchronous (8/16-bit bus width) SRAM,<br>Flash (NOR, NAND),<br>SDRAM and Mobile SDRAM (16-bit bus width) <sup>(1)</sup>                                  |  |  |  |  |

| (for more detail, see the<br>Device Configuration<br>section).           | DMA                                        |                   | Four DMA controllers each with four channels,<br>for a total of 16 channels                                                                                |  |  |  |  |

|                                                                          | Timers                                     |                   | 2 32-Bit General-Purpose (GP) Timers<br>1 Additional Timer Configurable as a 32-Bit GP Timer and/or a<br>Watchdog                                          |  |  |  |  |

|                                                                          | UART                                       |                   | 1 (with RTS/CTS flow control)                                                                                                                              |  |  |  |  |

|                                                                          | SPI                                        |                   | 1 with 4 chip selects                                                                                                                                      |  |  |  |  |

|                                                                          | I <sup>2</sup> C                           |                   | 1 (Master/Slave)                                                                                                                                           |  |  |  |  |

|                                                                          | l <sup>2</sup> S                           |                   | 4 (Two Channel, Full Duplex Communication)                                                                                                                 |  |  |  |  |

|                                                                          | USB 2.0 (Device only)                      |                   | High- and Full-Speed Device                                                                                                                                |  |  |  |  |

|                                                                          | MMC/SD                                     |                   | 2 MMC/SD, 256 byte read/write buffer, max 50-MHz clock for<br>SD cards, and signaling for DMA transfers                                                    |  |  |  |  |

|                                                                          | LCD Bridge                                 |                   | 1 (8-bit or 16-bit asynchronous parallel bus)                                                                                                              |  |  |  |  |

|                                                                          | ADC (Successive Approxi                    | mation [SAR])     | 1 (10-bit, 4-input, 16-µs conversion time)                                                                                                                 |  |  |  |  |

|                                                                          | Real-Time Clock (RTC)                      |                   | 1 (Crystal Input, Separate Clock Domain and Power Supply                                                                                                   |  |  |  |  |

|                                                                          | FFT Hardware Accelerato                    | r                 | 1 (Supports 8 to 1024-point 16-bit real and complex FFT)                                                                                                   |  |  |  |  |

|                                                                          | General-Purpose Input/Ou                   | utput Port (GPIO) | Up to 26 pins (with 1 Additional General-Purpose Output (XI<br>and 4 Special-Purpose Outputs for Use With SAR)                                             |  |  |  |  |

|                                                                          | Size (Bytes)                               |                   | 320KB RAM, 128KB ROM                                                                                                                                       |  |  |  |  |

| On-Chip Memory                                                           | Organization                               |                   | <ul> <li>64KB On-Chip Dual-Access RAM (DARAM)</li> <li>256KB On-Chip Single-Access RAM (SARAM)</li> <li>128KB On-Chip Single-Access ROM (SAROM)</li> </ul> |  |  |  |  |

| JTAG BSDL_ID                                                             | JTAGID Register<br>(Value is: 0x1B8F E02F) |                   | see Figure 5-45                                                                                                                                            |  |  |  |  |

|                                                                          | N411-                                      | 1.05-V Core       | 60 or 75 MHz                                                                                                                                               |  |  |  |  |

| CPU Frequency                                                            | MHz                                        | 1.3-V Core        | 100 or 120 MHz                                                                                                                                             |  |  |  |  |

| O tala Tita                                                              |                                            | 1.05-V Core       | 16.67, 13.3 ns                                                                                                                                             |  |  |  |  |

| Cycle Time                                                               | ns                                         | 1.3-V Core        | 10, 8.33 ns                                                                                                                                                |  |  |  |  |

|                                                                          | 0                                          |                   | 1.05 V (60, 75 MHz)                                                                                                                                        |  |  |  |  |

| Voltage                                                                  | Core (V)                                   |                   | 1.3 V (100, 120 MHz)                                                                                                                                       |  |  |  |  |

|                                                                          | I/O (V)                                    |                   | 1.8 V, 2.5 V, 2.75 V, 3.3 V                                                                                                                                |  |  |  |  |

| LDOs                                                                     | DSP_LDO                                    |                   | 1.3 V or 1.05 V, 250 mA max current for DSP CPU (CV <sub>DD</sub> )                                                                                        |  |  |  |  |

|                                                                          | ANA_LDO                                    |                   | 1.3 V, 4 mA max current for PLL (V <sub>DDA_PLL</sub> ), SAR, and power management circuits (V <sub>DDA_ANA</sub> )                                        |  |  |  |  |

|                                                                          | USB_LDO                                    |                   | 1.3 V, 25 mA max current for USB core digital (USB_V <sub>DD1P3</sub> )<br>and PHY circuits (USB_V <sub>DD1P3</sub> )                                      |  |  |  |  |

| PLL Options                                                              | Software Programmable N                    | Aultiplier        | x4 to x4099 multiplier                                                                                                                                     |  |  |  |  |

| BGA Package                                                              | 10 x 10 mm                                 |                   | 196-Pin BGA (ZCH)                                                                                                                                          |  |  |  |  |

Table 2-1. Characteristics of the C5515 Processor

(1) For more information on SDRAM devices support, see Section 5.9, External Memory Interface (EMIF).

7

SPRS645F - AUGUST 2010 - REVISED OCTOBER 2013

Texas Instruments

www.ti.com

#### Table 2-1. Characteristics of the C5515 Processor (continued)

| HA                            | RDWARE FEATURES                                                               | C5515   |

|-------------------------------|-------------------------------------------------------------------------------|---------|

| Process Technology µm         |                                                                               | 0.09 µm |

| Product Status <sup>(2)</sup> | Product Preview (PP),<br>Advance Information (AI),<br>or Production Data (PD) | PD      |

(2) PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

# 2.2 C55x CPU

The TMS320C5515 fixed-point digital signal processor (DSP) is based on the C55x CPU 3.3 generation processor core. The C55x DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, three data read buses (one 32-bit data read bus and two 16-bit data read buses), two 16-bit data write buses, and additional buses dedicated to peripheral and DMA activity. These buses provide the ability to perform up to four data reads and two data writes in a single cycle. Each DMA controller can perform one 32-bit data transfer per cycle, in parallel and independent of the CPU activity.

The C55x CPU provides two multiply-accumulate (MAC) units, each capable of 17-bit x 17-bit multiplication in a single cycle. A central 40-bit arithmetic/logic unit (ALU) is supported by an additional 16-bit ALU. Use of the ALUs is under instruction set control, providing the ability to optimize parallel activity and power consumption. These resources are managed in the Address Unit (AU) and Data Unit (DU) of the C55x CPU.

The C55x DSP generation supports a variable byte width instruction set for improved code density. The Instruction Unit (IU) performs 32-bit program fetches from internal or external memory, stores them in a 128-byte Instruction Buffer Queue, and queues instructions for the Program Unit (PU). The Program Unit decodes the instructions, directs tasks to AU and DU resources, and manages the fully protected pipeline. Predictive branching capability avoids pipeline flushes on execution of conditional instruction calls.

For more detailed information on the CPU, see the *TMS320C55x CPU 3.0 CPU* Reference Guide (literature number SWPU073).

The C55x core of the device can address 16M bytes of unified data and program space. It also addresses 64K words of I/O space and includes three types of on-chip memory: 128 KB read-only memory (ROM), 256 KB single-access random access memory (SARAM), 64 KB dual-access random access memory (DARAM). The memory map is shown in Figure 2-1.

## 2.2.1 On-Chip Dual-Access RAM (DARAM)

The DARAM is located in the byte address range 000000h – 00FFFFh and is composed of eight blocks of 4K words each (see Table 2-2). Each DARAM block can perform two accesses per cycle (two reads, two writes, or a read and a write). The DARAM can be accessed by the internal program, data, or DMA buses.

| CPU<br>BYTE ADDRESS RANGE | DMA CONTROLLER<br>BYTE ADDRESS RANGE | MEMORY BLOCK           |

|---------------------------|--------------------------------------|------------------------|

| 000000h – 001FFFh         | 0001 0000h – 0001 1FFFh              | DARAM 0 <sup>(1)</sup> |

| 002000h – 003FFFh         | 0001 2000h – 0001 3FFFh              | DARAM 1                |

| 004000h – 005FFFh         | 0001 4000h – 0001 5FFFh              | DARAM 2                |

| 006000h – 007FFFh         | 0001 6000h – 0001 7FFFh              | DARAM 3                |

| 008000h – 009FFFh         | 0001 8000h – 0001 9FFFh              | DARAM 4                |

| 00A000h – 00BFFFh         | 0001 A000h – 0001 BFFFh              | DARAM 5                |

| 00C000h - 00DFFFh         | 0001 C000h – 0001 DFFFh              | DARAM 6                |

| 00E000h – 00FFFFh         | 0001 E000h – 0001 FFFFh              | DARAM 7                |

(1) The first 192 bytes are reserved for memory-mapped registers (MMRs). See Figure 2-1, Memory Map Summary.

SPRS645F - AUGUST 2010 - REVISED OCTOBER 2013

# 2.2.2 On-Chip Single-Access RAM (SARAM)

The SARAM is located at the byte address range 010000h – 04FFFFh and is composed of 32 blocks of 4K words each (see Table 2-3). Each SARAM block can perform one access per cycle (one read or one write). SARAM can be accessed by the internal program, data, or DMA buses. SARAM is also accessed by the USB and LCD DMA buses.

| CPU<br>BYTE ADDRESS RANGE | DMA/USB CONTROLLER<br>BYTE ADDRESS RANGE | MEMORY BLOCK            |

|---------------------------|------------------------------------------|-------------------------|

| 010000h - 011FFFh         | 0009 0000h – 0009 1FFFh                  | SARAM 0                 |

| 012000h - 013FFFh         | 0009 2000h – 0009 3FFFh                  | SARAM 1                 |

| 014000h - 015FFFh         | 0009 4000h – 0009 5FFFh                  | SARAM 2                 |

| 016000h - 017FFFh         | 0009 6000h – 0009 7FFFh                  | SARAM 3                 |

| 018000h - 019FFFh         | 0009 8000h – 0009 9FFFh                  | SARAM 4                 |

| 01A000h - 01BFFFh         | 0009 A000h – 0009 BFFFh                  | SARAM 5                 |

| 01C000h - 01DFFFh         | 0009 C000h – 0009 DFFFh                  | SARAM 6                 |

| 01E000h - 01FFFFh         | 0009 E000h – 0009 FFFFh                  | SARAM 7                 |

| 020000h - 021FFFh         | 000A 0000h – 000A 1FFFh                  | SARAM 8                 |

| 022000h - 023FFFh         | 000A 2000h – 000A 3FFFh                  | SARAM 9                 |

| 024000h - 025FFFh         | 000A 4000h – 000A 5FFFh                  | SARAM 10                |

| 026000h - 027FFFh         | 000A 6000h – 000A 7FFFh                  | SARAM 11                |

| 028000h - 029FFFh         | 000A 8000h – 000A 9FFFh                  | SARAM 12                |

| 02A000h - 02BFFFh         | 000A A000h – 000A BFFFh                  | SARAM 13                |

| 02C000h - 02DFFFh         | 000A C000h – 000A DFFFh                  | SARAM 14                |

| 02E000h - 02FFFFh         | 000A E000h – 000A FFFFh                  | SARAM 15                |

| 030000h - 031FFFh         | 000B 0000h – 000B 1FFFh                  | SARAM 16                |

| 032000h - 033FFFh         | 000B 2000h – 000B 3FFFh                  | SARAM 17                |

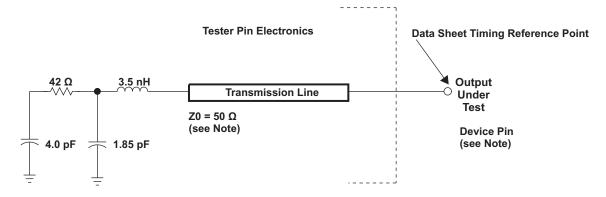

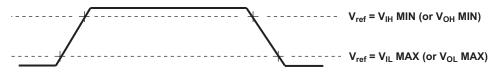

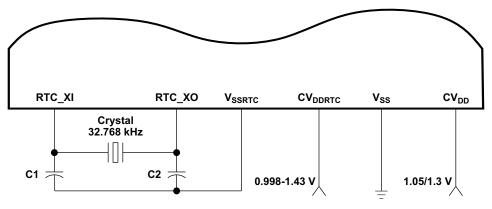

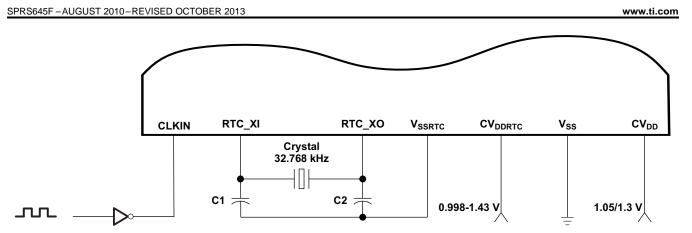

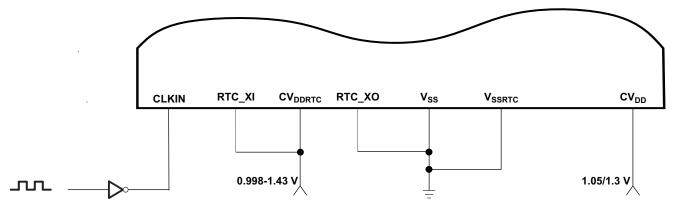

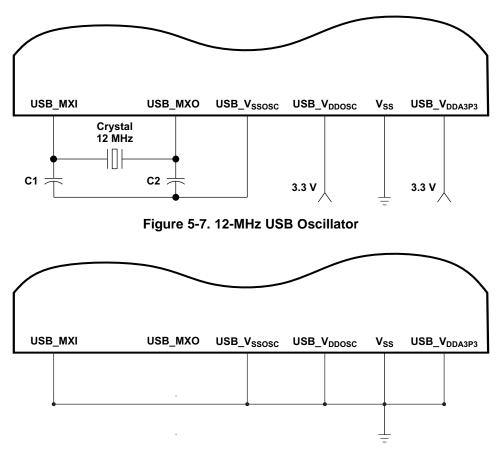

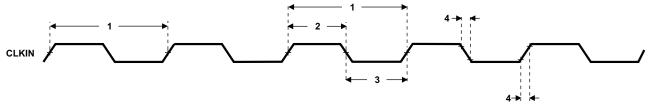

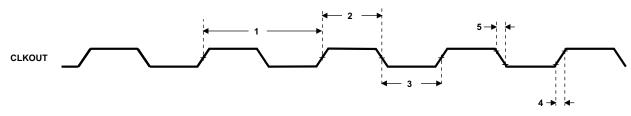

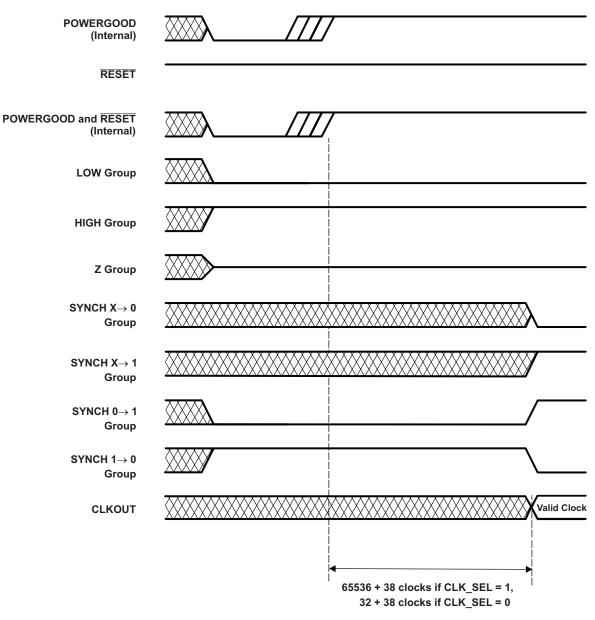

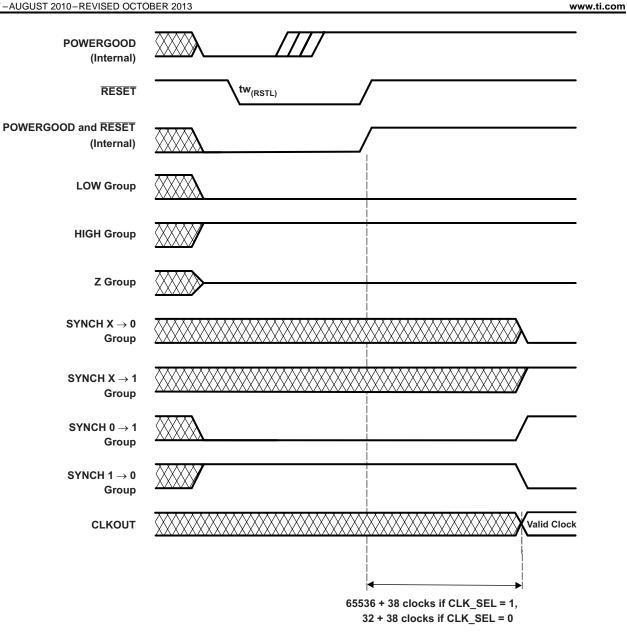

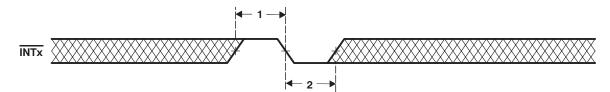

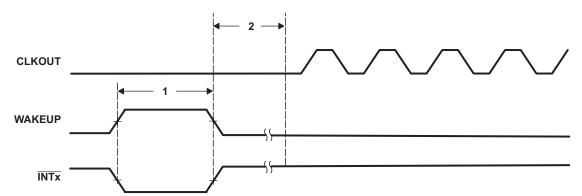

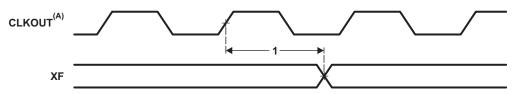

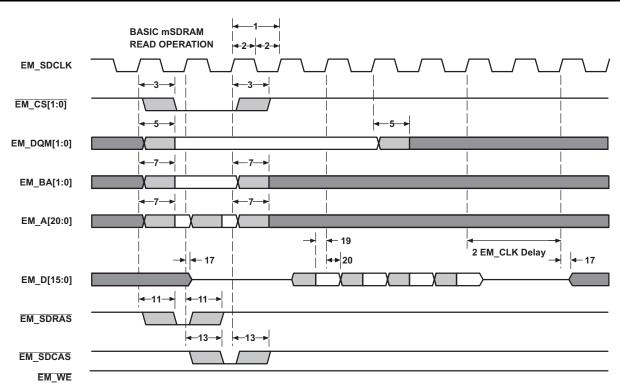

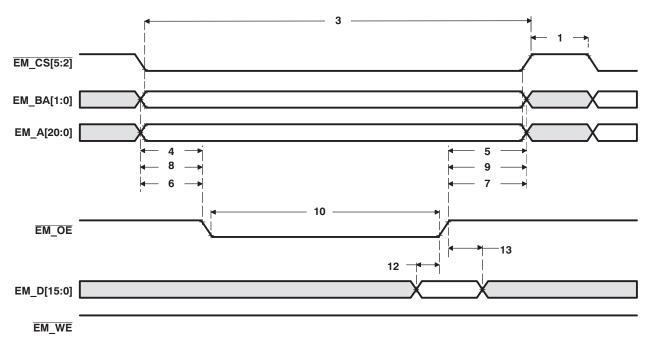

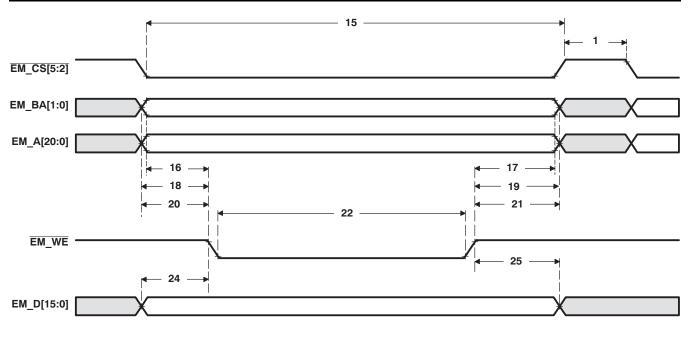

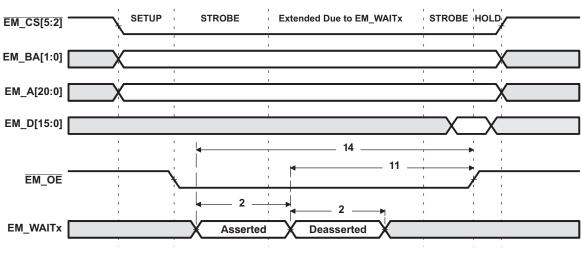

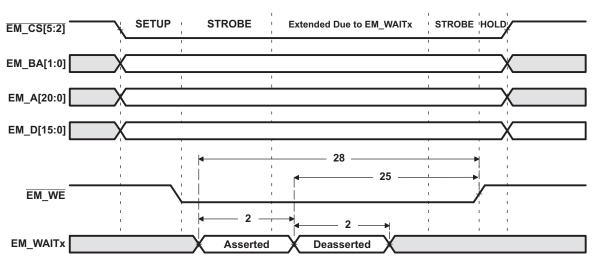

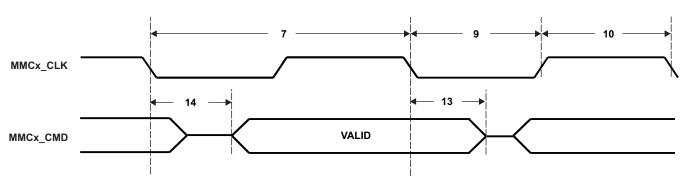

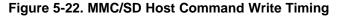

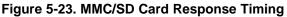

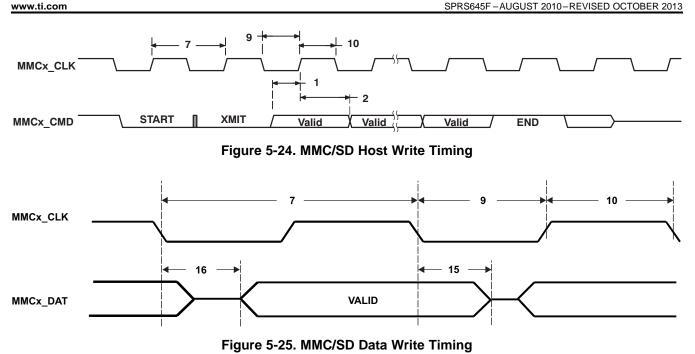

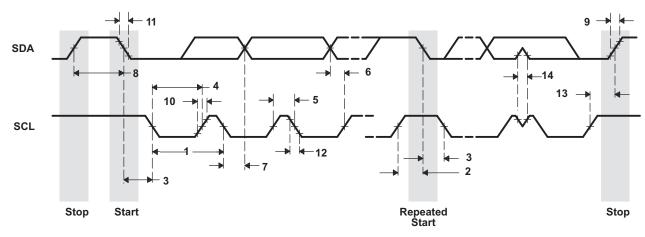

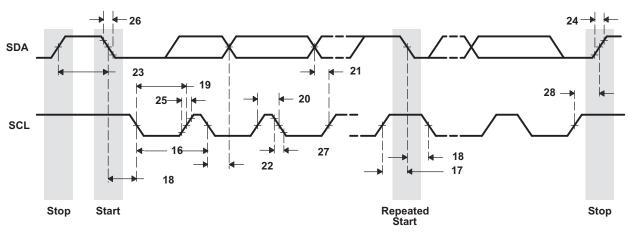

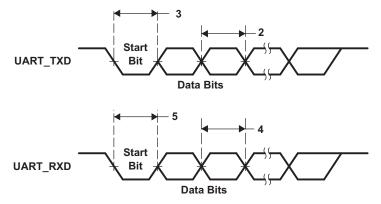

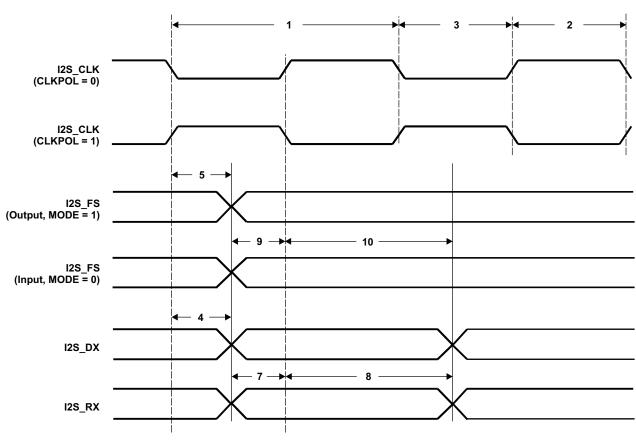

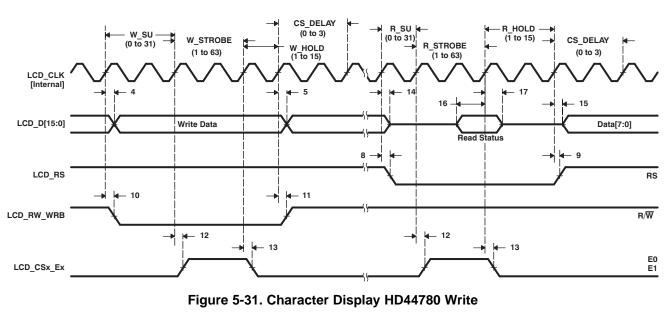

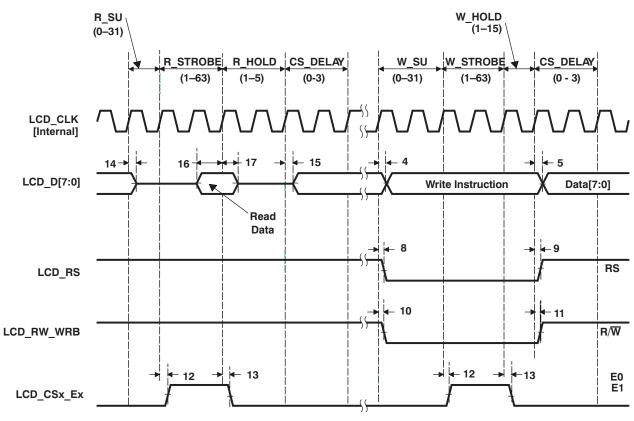

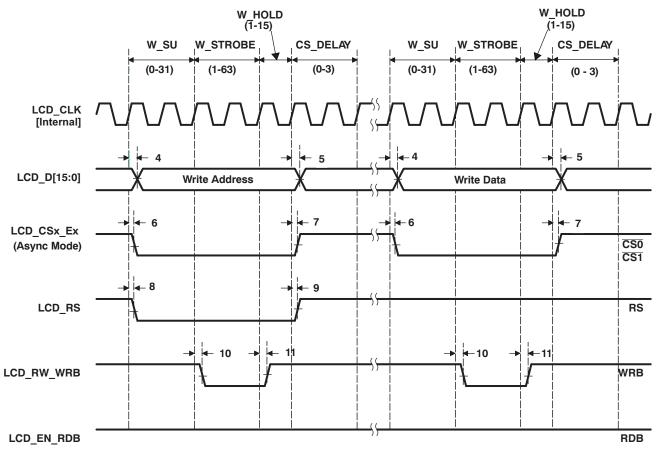

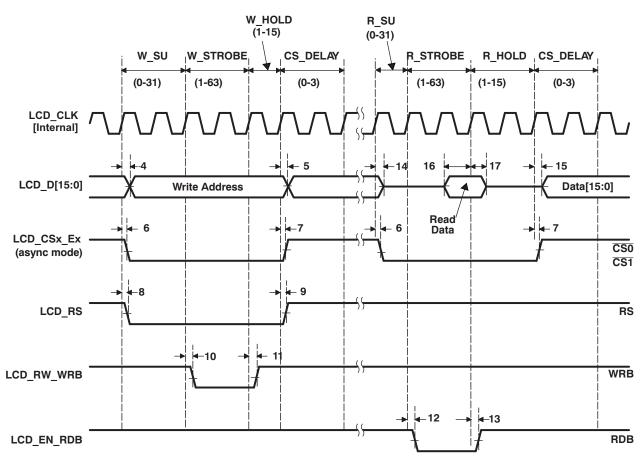

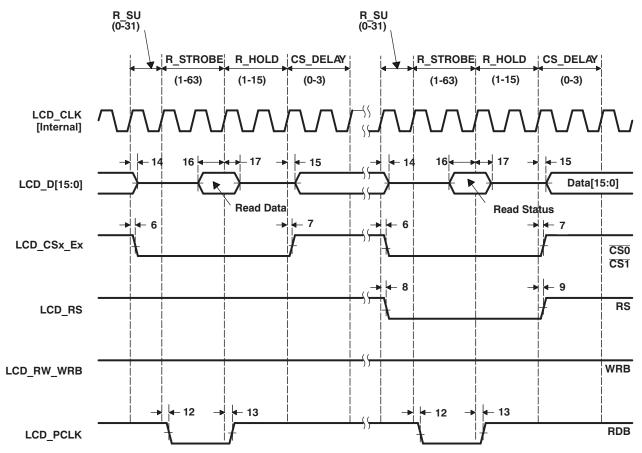

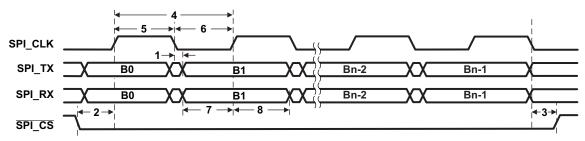

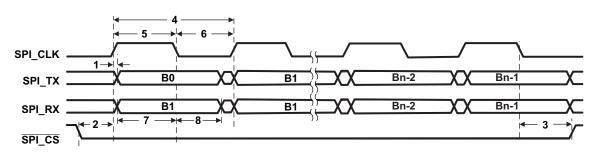

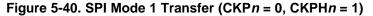

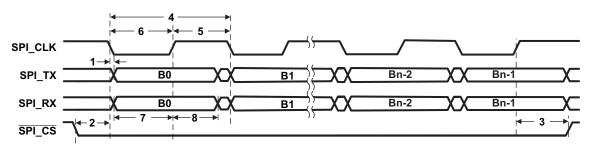

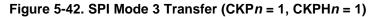

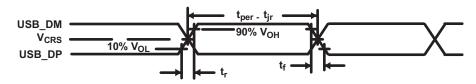

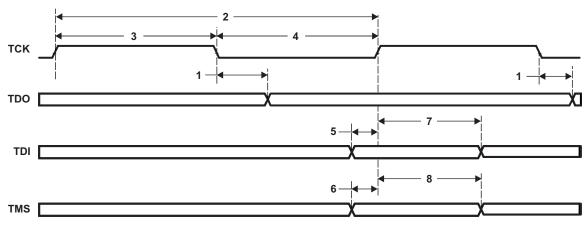

| 034000h - 035FFFh         | 000B 4000h – 000B 5FFFh                  | SARAM 18                |